Audits. The mere mention of the word keeps project managers up at night and sends most designers running. However, in the case of FPGA designs seeking DO-254 compliance, the product doesn’t ship until the audit is complete – there is no avoiding it, or skating around it.… Read More

5nm Chips? Yes, but When?

For any invention, technical proof of concept or prototyping happens years ahead of the invention being infused into actual products. When we talk about 5nm chip manufacturing, a test chip was already prototyped in last October, thanks to Cadence and Imec. Details about this chip can be found in a blog at Semiwiki (link is given … Read More

Should there be a 5-second IoT chip rule?

Kids have a tendency to put things in their mouths. Any parent can relate to the statement, “Put that down! You don’t know where it’s been!” After the first child, concern usually relaxes quite a bit. People joke about a 5-second rule on the premise if an object was just dropped on the floor, it may not be contaminated yet.… Read More

3 flavors of TMR for FPGA protection

Back in the microprocessor stone age, government procurement agencies fell in love with the idea of radiation hardened parts that might survive catastrophic events. In those days, before rad-hard versions of PowerPC and SPARC arrived, there were few choices for processors in defense and space programs.

One of the first rad-hard… Read More

The Twists and Turns of Xilinx vs Altera!

The battle between Xilinx and Altera continues to be one of the more interesting stories to cover. It really is the semiconductor version of a reality TV show. In the beginning it was two fabless companies partnered with rival foundries going head-to-head controlling a single market that touches a variety of industries.

Then things… Read More

5 ways FPGA-based prototyping shrinks design time

Engineers are trained to think linearly, along the lines of we started here, then we did this, and that, and this other stuff, and here is where we ended up. If you’ve ever presented in an internal review meeting, sales conference, or a TED-like event, you know that is a dangerous strategy in winning friends and influencing people.… Read More

HLS with ARM and FPGA Technologies Boosts SoC Performance

The way SoC size and complexity are increasing; new ways of development and verification are also evolving with innovative automated tools and environment for SoC development and optimization. IP based SoC development methodology has proved to be the most efficient for large SoCs. This needs collaboration among multiple players… Read More

Breaking the Limits of SoC Prototyping

Earlier this month during my conversation with Dr. Walden C. Rhines, he emphasised the need for our next generation designers to think at system level and design everything keeping the system’s view in mind. The verification will go through major transformation at the system level. I can see the FPGA prototyping systems already… Read More

Pushing on AXI-connected IP in FPGAs

Success stories are great. Reading how someone uses a product contributes much more insight than reading about a product. Last month we had a teaser for a presentation by Wave Semiconductor; this month, we have the slides showing how they are using FPGA-based prototyping, AXI transactions, and DPI to speed up development.

First,… Read More

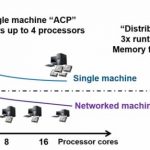

Why FPGA synthesis with Synplify is now faster

The headline of the latest Synopsys press release drops quite a tease: the newest release of Synplify delivers up to 3x faster runtime performance in FPGA synthesis. In our briefing for this post, we uncovered the surprising reason why – and it’s not found in their press release.… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center