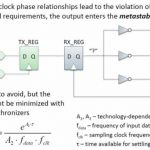

Many tools find clock domain crossings (CDCs) in FPGA designs. Some don’t find the right ones since they don’t comprehend things like in-house synchronizer constructs. Some find too many based on misunderstanding intent, inaccurate constraints, and other factors that lead to noise.… Read More

VHDL parameterized PWM controller

Digital outputs can either go ON or OFF. Analog signals, on the other side, can smoothly assume multiple values in a range. There is a technique that emulates analog behavior with a digital output. That technique is PWM, namely, Pulse Width Modulation. It can be implemented as pulses with varying ‘high’ and ‘low’… Read More

Intel Stratix 10 MX FPGA Highlights

These days, FPGAs are fairly complex pieces of silicon. Being that the case, it would take several articles even to put a summary of the features embedded in high-end FPGA devices. Hence, in this article, I will concentrate in just one feature, namely, the new embedded memory blocks of the recently released Intel-Altera Stratix… Read More

Mentor Functional Verification Study 2016

Periodically, Mentor commissions a user/usage survey on Functional Verification, conducted by the Wilson Research Group, then they publish the results to all of us, an act of industry good-citizenship for which I think we owe them a round of thanks. Harry Foster at Mentor is breaking down the report into a series of 15 blogs. He’s… Read More

SoC FPGAs for IoT Edge Computing

One of the reasons for the explosive growth of IoT is that embedded devices with networking capabilities and sensor interfaces are cheap enough to deploy them at a plethora of locations.

However, network bandwidth is limited. Not only that, but also, the latency of the network can be of seconds or minutes. By the time the sensor data… Read More

FPGAs at Deep Machine Learning

The concept of machine learning is not new. Attempts at systems emulating intelligent behavior, like expert systems, go as far back as the early 1980’s. And the very notion of modern Artificial Intelligence has a long history. The name itself was coined at a Dartmouth College conference (1956), but the idea of an “electronic… Read More

Keeping your design files organized

Men marry women wishing they will never change, but they do.Women marry men wishing they will be able to change them, but they don’t.

When I was young, even during my University studies, I was a real disaster in anything related to order. My room was always a mess. Whenever my mother or any other would try to change my ways (even… Read More

Pseudo random generator tutorial in VHDL (Part 3/3)

On the first two chapters of this Tutorial we started with a simple LFSR module and added a test bench. Then, on chapters three and four we upgraded our module with some features and learned to export the test bench data to files.

… Read More

Pseudo random generator tutorial in VHDL (Part 2/3)

In the first part of this tutorialwe started with a simple implementation of an LFSR block (Chapter 1) and its test bench (Chapter 2). Let’s make our code look a bit more professional.

… Read More

Pseudo random generator tutorial in VHDL (Part 1/3)

In this tutorial we will see how to design a VHDL block. We will start with a very simple block and we will gradually add features to it. We will also simulate it and test its output with Matlab. Over the process we will see:

… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center