Writing a white paper is never tedious, and when the product or the technology is emerging, it can become fascinating. Like for this white paper I have written for Menta “How Standard Cell Based eFPGA IP are Offering Maximum Flexibility to New System-on-Chip Generation”. eFPGA technology is not really emerging, but it’s fascinating… Read More

How standard-cell based eFPGA IP can offer maximum safety, flexibility and TTM?

Writing a white paper is never tedious, and when the product or the technology is emerging, it can become fascinating. Like for this white paper I have written for Menta “How Standard Cell Based eFPGA IP are Offering Maximum Flexibility to New System-on-Chip Generation”. eFPGA technology is not really emerging, but it’s fascinating… Read More

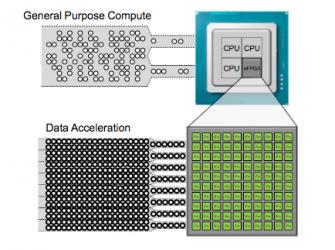

Accelerating Accelerators

Accelerating compute-intensive software functions by moving them into hardware has a long history, stretching back (as far as I remember) to floating-point co-processors. Modern SoCs are stuffed with these applications, from signal processors, to graphics processors, codecs and many more functions. All of these accelerators… Read More

An IIot Gateway to the Cloud

A piece of learning we all seem to have gained from practical considerations of IoT infrastructure is that no, it doesn’t make sense to ship all the data from an IoT edge device to the cloud and let the cloud do all the computational heavy lifting. On the face of it that idea seemed good – all those edge devices could be super cheap (silicon… Read More

Partitioning for Prototypes

I earlier wrote a piece to make you aware of a webinar to be hosted by Aldec on some of their capabilities for partitioning large designs for prototyping. That webinar has now been broadcast and I have provided a link to the recorded version at the end of this piece. The webinar gets into the details of how exactly you would use the software… Read More

Embedded FPGA IP as a Post-Silicon Debugger

The hardware functionality of a complex SoC is difficult to verify. Embedded software developed for a complex, multi-core SoC is extremely difficult to verify. An RTOS may need to be ported and validated. Application software needs to be developed, and optimized for performance. Sophisticated methodologies are employed to… Read More

Webinar: Aiding ASIC Design Partitioning for multi-FPGA Prototyping

The advantages of prototyping a hardware design on a FPGA platform are widely recognized, for software development, debug and regression in particular while the ultimate ASIC hardware is still in development. And if your design will fit into a single FPGA, this is not an especially challenging task (as long as you know your way … Read More

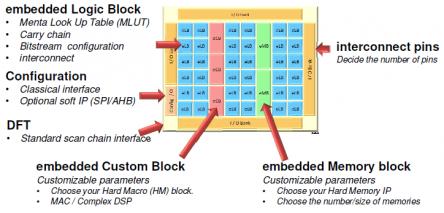

Embedding FPGA IP

The appeal of embedding an FPGA IP in an ASIC design is undeniable. For much of your design, you want all the advantages of ASIC: up to GHz performance, down to mW power (with active power management), all with very high levels of integration with a broad range of internal and 3[SUP]rd[/SUP]-party IP (analog/RF, sensor fusion, image/voice… Read More

A Functional Safety Primer for FPGA – the White Paper

Following up on their webinar on functional safety in FPGA-based designs, Synopsys have now published a white paper expanding on some of those topics. For those who didn’t get a chance to see the webinar this blog follows the white paper flow and is similar but not identical to my webinar blog, particularly around differences between… Read More

Webinar: Fast-Track to Riviera-PRO

Whether you’re right out of college, starting on your first design, a burn-and-churn designer thinking there must be a better way or an ASIC designer wanting to do a little prototyping, this webinar may be for you. It’s a fast start on using the Aldec Riviera-PRO platform for verification setup, run and debug, and more. There are … Read More

From the Selfie to Samantha: The Next Trillion-Dollar Behavior