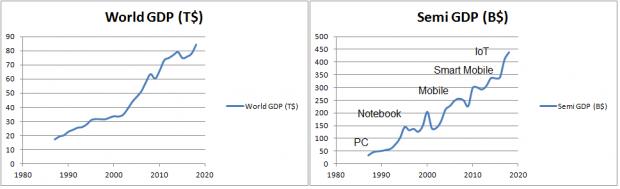

At TSMC 2018 Silcon Valley Technology Symposium, Dr Kevin Zhang, TSMC VP of Business Development covered technology updates for IoT platform. The three growth drivers in this segment namely TSMC low power, RF enhancement and embedded memory technology (MRAM/RRAM) reinforced both progress and growth in global semiconductor… Read More

TSMC Technologies for Mobile and HPC

During TSMC 2018 Technology Symposium, Dr. B.J. Woo, TSMC VP of Business Development presented market trends in the area of mobile applications and HPC computing as well as shared TSMC progress in making breakthrough efforts in the technology offerings to serve these two market segments.

Both 5G and AI are taking the center stage… Read More

Top 10 Highlights of the TSMC 2018 Technology Symposium

Here are the Top 10 highlights from the recent TSMC 2018 Technology Symposium, held in Santa Clara CA. A couple of years ago, TSMC acknowledged the unique requirements of 4 different market segments, which has since guided their process development strategy — Mobile, High-Performance Computing (HPC), Automotive, and… Read More

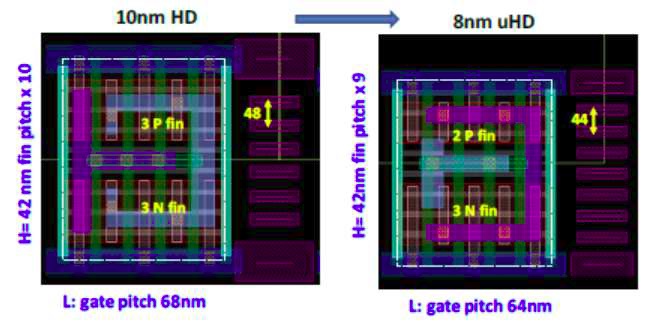

Samsung 10nm 8nm and 7nm at VLSIT

I got a tip sheet today for the upcoming 2018 Symposia on VLSI Technology & Circuits to be held June 19th through 21st in Honolulu, Hawaii. There is some interesting information on Samsung’s 10nm, 8nm and 7nm processes in the tip sheet:… Read More

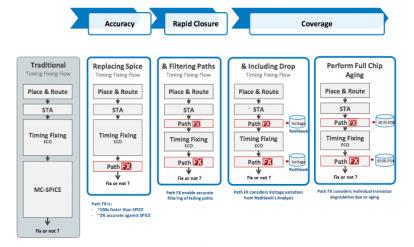

Peering Over the Timing Edge

I wrote recently about a yield problem which mobile vendors have been finding for devices built in advanced technologies. This was a performance issue (the devices worked fine at lower clock speeds), pointing to a discrepancy in some devices between predicted and observed timing. These were experienced design teams, using state… Read More

imec and Cadence on 3nm

One of the more frequent questions I get, “What is next after FinFETs?” is finally getting answered. Thankfully I am surrounded by experts in the process technology field including Scotten Jones of IC Knowledge. I am also surrounded by design enablement experts so I really am the man in the middle which brings us to a discussion between… Read More

Intel 10nm Yield Issues

On their first quarter earnings call Intel announced that volume production of 10nm has been moved from the second half of 2018 to 2019 due to yield issues. Specifically, they are shipping 10nm in low volume now, but yield improvement has been slower than anticipated. They report that they understand the yield issues but that improvements… Read More

Monitoring Process, Voltage and Temperature in SoCs, webinar recap

Have you ever wondered how process variation, thermal self-heating and Vdd levels affect the timing and yield of your SoC design? If you’re clock specification calls for 3GHz, while your silicon is only yielding at 2.4GHz, then you have a big problem on your hands. Such are the concerns of many modern day chip designers. To… Read More

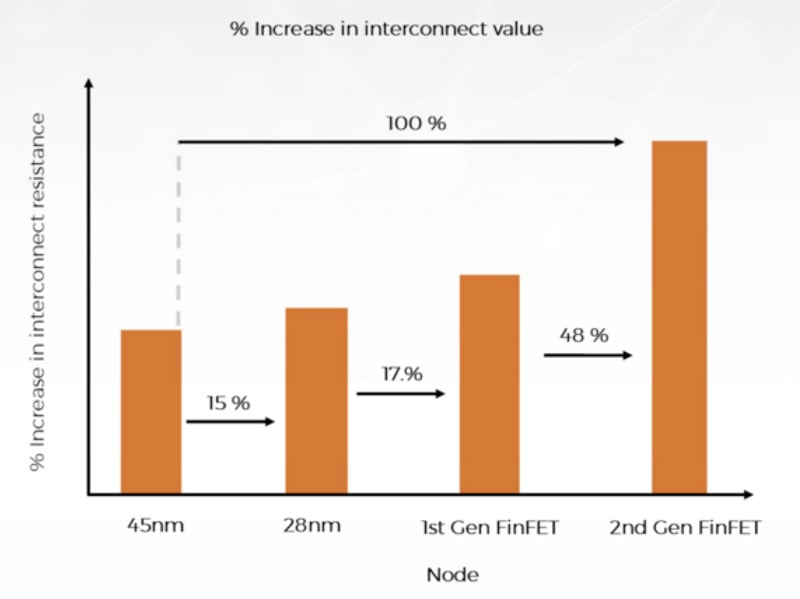

Sometimes a Solver is a Suitable Solution

Traditional, rule based, RC extractors rely on a substantial base of assumptions, which are increasingly proving unreliable. Having accurate RC extraction results for parasitic R’s and C’s is extremely important for ensuring proper circuit operation and for optimizing performance and power. Advanced process nodes are making… Read More

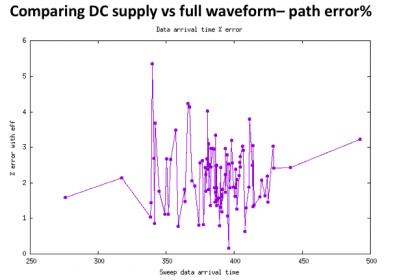

A New Problem for High-Performance Mobile

About 6 months ago, ANSYS was approached by a couple of leading mobile platform vendors/suppliers with a challenging problem. These companies were hitting target 2.5GHz performance goals on their (N10 or N7) application processors, but getting about 10% lower yield than expected, which they attributed to performance failures.… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center