To meet the increased demand for converter speed and resolution, JEDEC proposed the JESD204 standard describing a new efficient serial interface to handle data converters. In 2006, the JESD204 standard offered support for multiple data converters over a single lane with the following standard revisions; A, B, and C successively… Read More

TSMC Earnings – The Handoff from Mobile to HPC

Hello! The most important semiconductor company in the world reported earnings last night. It’s been something of a tradition to post Taiwan Semiconductor Company (TSMC) earnings posts not behind my paywall, and I think that I’m going to continue that to kickoff each earnings season.

There are so many threads in the TSMC call that… Read More

Webinar: Investing in Semiconductor Startups

Investing in semiconductor startups is something Silicon Catalyst knows a lot about. During a time when venture funding for chip companies all but disappeared, this remarkable organization built a robust incubator, ecosystem, support infrastructure and funding source. Silicon Catalyst has assembled a top-notch management… Read More

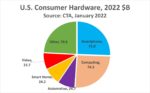

CES is Back – Partially

CES (formerly the Consumer Electronics Show) returned to Las Vegas, Nevada last week. In 2021, CES was remote due to the COVID-19 pandemic. On April 28, 2021, the Consumer Technology Association (CTA), the sponsor of CES, announced CES 2022 would be held in Las Vegas. On the date of the announcement new COVID cases in the U.S. were… Read More

DAC 2021 – What’s Up with Agnisys and Spec-driven IC Development

Walking the exhibit floors at DAC in December I spotted the familiar face of Anupam Bakshi, Founder and CEO of Agnisys, so I stopped by the booth to get an update on his EDA company. My first question for him was about the origin of the company name, Agnisys, and I found at that Agni means Fire in Sanskrit, one of the five elements.

The … Read More

IBM at IEDM

IBM transferred their semiconductor manufacturing to GLOBALFOUNDRIES several years ago but still maintains a multibillion-dollar research facility at Albany Nanotech. IBM is very active at conferences such as IEDM and appears to have a good public relations department because they get a lot of press.

At the Litho Workshop … Read More

CES 2022 and the Electrification of Cycling

With the Omicron variant of the COVID-19 virus in the news, there have been some big corporate names withdrawing from CES ( Peleton, Super73), however the cycling innovation companies assembled once again in Las Vegas this year for CES 2022. Data from statista show the strong growth in bicycle revenues in March 2020, when the pandemic… Read More

Self-Aligned Via Process Development for Beyond the 3nm Node

The further scaling of interconnect and via lithography for advanced nodes is challenged by the requirement to provide a process window that supports post-patterning critical dimension variations and mask overlay tolerances. At the recent international Electron Devices Meeting (IEDM) in San Francisco, TSMC presented … Read More

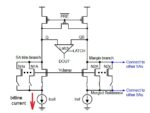

Technology Design Co-Optimization for STT-MRAM

Previous SemiWiki articles have described the evolution of embedded non-volatile memory (eNVM) IP from (charge-based) eFlash technology to alternative (resistive) bitcell devices. (link, link)

The applications for eNVM are vast, and growing. For example, microcontrollers (MCUs) integrate non-volatile memory for … Read More

Demand for High Speed Drives 200G Modulation Standards

Right now, the most prevalent generation of Ethernet for data centers is 400 Gbps, with the shift to 800 Gbps coming rapidly. It is expected that by 2025 there will be 25 million units of 800 Gbps shipped. Line speeds of 100G are used predominantly for 400 Gbps Ethernet – requiring 4 lanes each. Initially 800 Gbps will simply … Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center