“Inverse lithography technology (ILT) represents the most significant EDA advance in the last two decades.” Danping Peng from TSMC made that assertion at the recent SPIE Advanced Lithography + Patterning Conference, in his talk entitled: ILT for HVM: History, Present, and Future. This article summarizes the highlights… Read More

Unlock first-time-right complex photonic integrated circuits

The capacity and energy efficiency challenges from the growing appetite for high-speed data along with advanced applications such as LIDAR and quantum computing are driving demand for increasingly large-scale photonic integrated circuits (PIC). With an ever-increasing number of components on a single photonic chip, manual… Read More

0.55 High-NA Lithography Update

At the recent SPIE Advanced Lithography + Patterning Conference, Mark Phillips from Intel gave an insightful update on the status of the introduction of the 0.55 high numerical aperture extreme ultraviolet lithography technology. Mark went so far as to assert that the development progress toward high-NA EUV would support … Read More

Using EM/IR Analysis for Efinix FPGAs

I’ve been following the EM/IR (Electro-Migration, IR is current and resistance) analysis market for many years now, and recently attended a presentation from Steven Chin, Sr. Director IC Engineering of Efinix, at the User2User event organized by Siemens EDA. The Tuesday presentation was in the morning at the Marriott… Read More

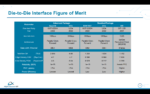

Die-to-Die IP enabling the path to the future of Chiplets Ecosystem

The topic of chiplets is getting a lot of attention these days. The chiplet movement has picked up more momentum since Moore’s law started slowing down as process technology approached 5nm. With the development cost of a monolithic SoC crossing the $500M and wafer yields of large die-based chips dropping steeply, the decision … Read More

The New Normal for Semiconductor Manufacturing

One of the recent live events I attended was the 2022 GSA Silicon Leadership Summit on May 12th at the Santa Clara Convention Center (my favorite location). This was the first GSA live event in two years so it was a must attend gathering. This event targets semiconductor ecosystem executives (200+ people attended) so there were many… Read More

[WEBINAR] Secure your devices with PUF plus hardware root-of-trust

It’s a hostile world we live in, and cybersecurity of connected devices is a big concern. Attacks are rising rapidly, and vulnerabilities get exploited immediately. Supply chains are complex. Regulations are proliferating. Secrets don’t stay secrets for long – in fact, the only secret in a system with open-source algorithms… Read More

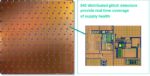

Sensing – Who needs it?

In a simple answer – everyone. A keynote presentation “Sensing the Unknowns and Managing Power” by Mahesh Tirupattur, the Executive Vice President at Analog Bits at the recent Siemens User2User conference, discussed the need and application of sensors in computing and power applications. Why sense? As Mahesh explains, sensing… Read More

Protecting High-Speed Interfaces in Data Centers with Security IP

The never ending appetite for higher bandwidths, faster data interfaces and lower latencies are bringing about changes in how data is processed at data centers. The expansion of cloud to the network edge has introduced broad use of artificial intelligence (AI) techniques for extracting meaning from data. Cloud supercomputing… Read More

Double Diffraction in EUV Masks: Seeing Through The Illusion of Symmetry

At this year’s SPIE Advanced Lithography conference, changes to EUV masks were particularly highlighted, as a better understanding of their behavior is becoming clear. It’s now confirmed that a seemingly symmetric EUV mask absorber pattern does not produce a symmetric image at the wafer, as a conventional DUV … Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center