In the old days to learn about new semiconductor IP you would have to schedule a sales call, listen to the pitch, then decide if the IP was promising or not. Today we have webinars which offer a lot less drama than a sales call, plus you get to ask your questions by typing away at the comfort of your desk, hopefully wearing headphones as … Read More

An Advanced-User View of Applied Formal

Thanks to my growing involvement in formal (at least in writing about it), I was happy to accept an invite to this year’s Oski DVCon dinner / Formal Leadership Summit. In addition to Oski folks and Brian Bailey (an esteemed colleague at another blog site, to steal a Frank Schirrmeister line), a lively group of formal users attended… Read More

Students Should Attend DAC in SFO

On LinkedIn I have some 2,116 connections and many of those are students looking to enter the field of EDA, IP or semiconductor design. What a wonderful opportunity these students have by attending the 55th annual DAC in San Francisco this summer from June 24-28. Technical sessions, keynote speeches, exhibitors, networking, … Read More

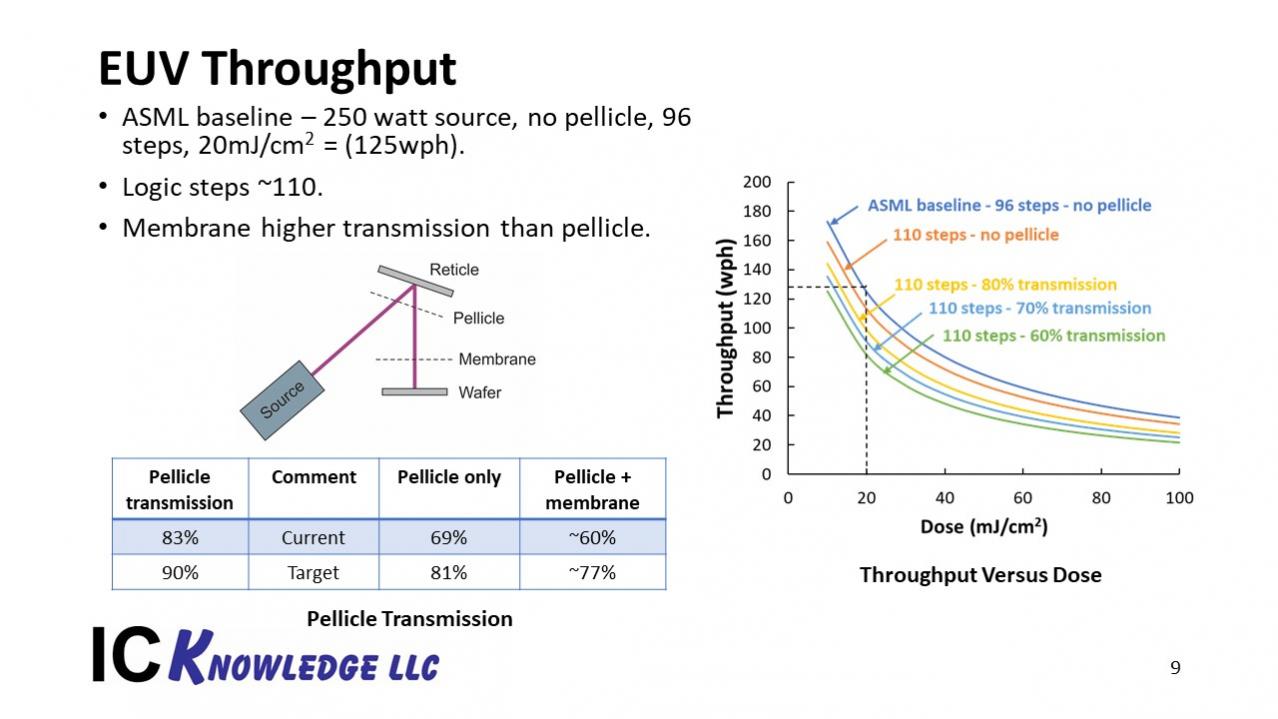

SPIE Advanced Lithography 2018 – EUV Status

This year the Advanced Lithography Conference felt very different to me than the last couple of years. I think it was Chris Mack who proclaimed it the year of Stochastics. EUV has dominated the conference for the last several years but in the past the conversation has been mostly centered on the systems, system power and uptime.

I … Read More

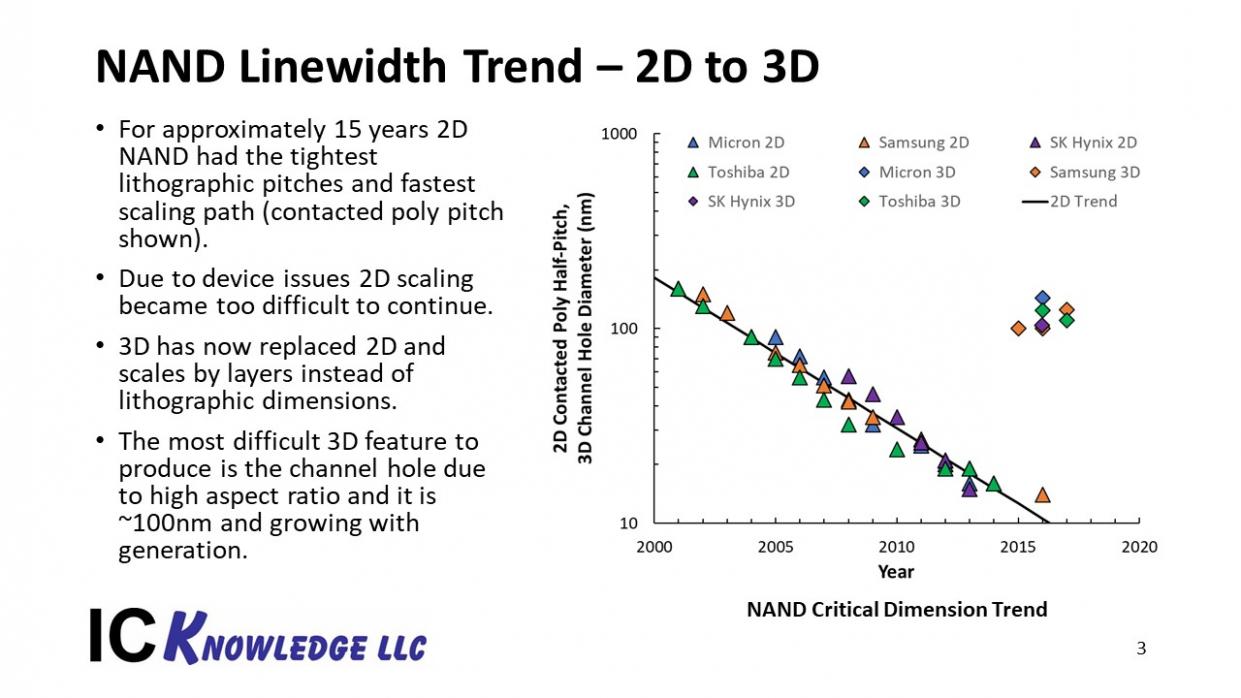

LithoVision 2018 The Evolving Semiconductor Technology Landscape and What it Means for Lithography

I was invited to present at Nikon’s LithoVision event held the day before the SPIE Advanced Lithography Conference in San Jose. The following is a write up of the talk I gave. In this talk I discuss the three main segments in the semiconductor industry, NAND, DRAM and Logic and how technology transitions will affect lithography.… Read More

Herb Reiter on the Challenges of 2.5D ASIC SiPs

Years ago my good friend Herb Reiter promoted the importance of 2.5D packaging to anybody and everybody who would listen including myself. Today Herb’s vision is in production and the topic of many papers, webinars, and conferences. According to Herb, and I agree completely, advanced IC packaging is an important technology for… Read More

SPIE 2018 Mentor Graphics Scott Jones and SemiWiki

Next week is SPIE, the leading lithography networking event here in Silicon Valley. Scott Jones is not only attending but also presenting at the 15th Annual LithoVision on Sunday. I will be at SPIE as well so if you want to meet up let us know. We will publish a blog on Scott’s presentation the morning of for those who cannot attend.… Read More

Free Webinar on Standard Cell Statistical Characterization

Variation analysis continues to be increasingly important as process technology moves to more advanced nodes. It comes as no surprise that tool development in this area has been vigorous and aggressive. New higher reliability IC applications, larger memory sizes and much higher production volumes require sophisticated yield… Read More

DVCon 2018 Mentor Graphics and SemiWiki

DVCon turns 30 this year which is a very big deal. My oldest child also turns 30 this year which really puts things in perspective looking back at what we have all accomplished during that time. DVCon originally started as a user’s group at the 1988 Design Automation Conference in Anaheim California and the rest as they say is history.… Read More

SPI Inspires a New Generation of SOC Designs

When I started dabbling in hardware again for fun using Arduinos about five years ago, it had been a long time since I had played with microprocessor chips. The epiphany for me was seeing how easy it was to load programs onto the onboard flash on something like an Atmel AVR using the SPI interface. My previous experience decades early… Read More

Captain America: Can Elon Musk Save America’s Chip Manufacturing Industry?