I don’t know if it was just me but I left TechCon 2017 feeling, well, uninspired. Not that they didn’t put on a good show with lots of announcements, but it felt workman-like. From anyone else it would have been a great show, but this is TechCon. I expect to leave with my mind blown in some manner and it wasn’t. I wondered if the SoftBank … Read More

Advanced Materials and New Architectures for AI Applications

Over the past 50 years in our industry, there have been three invariant principles:

- Moore’s Law drives the pace of Si technology scaling

- system memory utilizes MOS devices (for SRAM and DRAM)

- computation relies upon the “von Neumann” architecture

Technology Behind the Chip

Tom Dillinger and I attended the Silvaco SURGE 2018 event in Silicon Valley last week with several hundred of our semiconductor brethren. Tom has a couple blogs ready to go but first let’s talk about the keynote by Silvaco CEO David Dutton. David isn’t your average EDA CEO, he spent the first 8 years of his career at Intel then spent … Read More

ARM TechCon 2018 is Upon Us!

ARM TechCon is one of the most influential conferences in the semiconductor ecosystem without a doubt. This year ARM TechCon has moved from the Santa Clara Convention Center to the much larger convention center in San Jose. Last year the conference seemed to be busting at the seams so this move makes complete sense. A little less … Read More

How to Increase Energy Efficiency for IoT SoC?

If you have read the white paper recently launched by Dolphin, “New Power Management IP Solution from Dolphin Integration can dramatically increase SoC Energy Efficiency”, you should already know about the theory. This is a good basis to go further and discover some real-life examples, like Bluetooth Low Energy (BLE) chip in … Read More

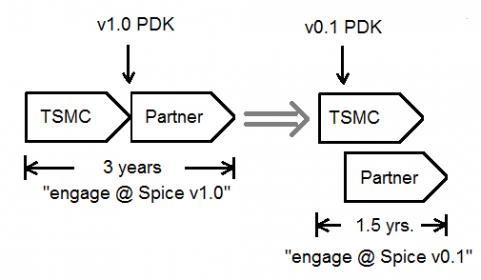

Top 10 Highlights from the TSMC Open Innovation Platform Ecosystem Forum

Each year, TSMC hosts two major events for customers – the Technology Symposium in the spring, and the Open Innovation Platform Ecosystem Forum in the fall. The Technology Symposium provides updates from TSMC on:

… Read More

AI and the Domain Specific Architecture

Last month I attended the 2018 U.S. Executive Forum where Wally Rhines was one of the keynotes. I was also lucky enough to have lunch with Wally afterwards and talk about his presentation in more detail and he sent me his slides which are attached to the end of this blog.

The nice thing about Wally’s presentations is that they are not … Read More

SURGE 2018 Silvaco Update!

The semiconductor industry has been very good to me over the past 35 years. I have had a front row seat to some of the most innovative and disruptive things like the fabless transformation and of course the Electronic Design Automation phenomenon, not to mention the end products that we as an industry have enabled. It is truly amazing… Read More

Custom SoC Platform Solutions for AI Applications at the TSMC OIP

The TSMC OIP event is next week and again it is packed with a wide range of technical presentations from TSMC, top semiconductor, EDA, and IP companies, plus long time TSMC partner and ASIC provider Open-Silicon, a SiFive Company. You can see the full agenda HERE.

AI is revolutionizing and transforming virtually every industry… Read More

IEDM Preview 2018

The International Electron Devices Meeting (IEDM) is one of the premier technical conferences covering semiconductor technology and is a must attend event. This years conference will be held December 1[SUP]st[/SUP] through 5th, 2018 at the Hilton San Francisco Union

Square hotel.… Read More

Captain America: Can Elon Musk Save America’s Chip Manufacturing Industry?