The annual SNUG (Synopsys Users Group) conference, now in its 35th year, once again brought together key stakeholders to showcase accomplishments, discuss challenges, and explore opportunities within the semiconductor and electronics industry. With approximately 2,500 attendees, SNUG 2025 served as a dynamic hub for collaboration… Read More

Podcast EP281: A Master Class in the Evolving Ethernet Standard with Jon Ames of Synopsys

Dan is joined by Jon Ames, principal product manager for the Synopsys Ethernet IP portfolio. Jon has been working in the communications industry since 1988 and has led engineering and marketing activities from the early days of switched Ethernet to the latest data center and high-performance computing Ethernet technologies.… Read More

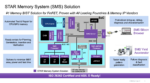

Evolution of Memory Test and Repair: From Silicon Design to AI-Driven Architectures

Memory testing in the early days of computing was a relatively straightforward process. Designers relied on simple, deterministic approaches to verify the functionality of memory modules. However, as memory density increased and systems became more complex, the likelihood of faults also rose. With advancements in memory… Read More

DVCon 2025: AI and the Future of Verification Take Center Stage

The 2025 Design and Verification Conference (DVCon) was a four-day event packed with insightful discussions, cutting-edge technology showcases, and thought-provoking debates. The conference agenda included a rich mix of tutorial sessions, a keynote presentation, a panel discussion, and an exhibit hall with Electronic… Read More

Synopsys Expands Hardware-Assisted Verification Portfolio to Address Growing Chip Complexity

Last week, Synopsys announced an expansion of their Hardware-Assisted Verification (HAV) portfolio to accelerate semiconductor design innovations. These advancements are designed to meet the increasing demands of semiconductor complexity, enabling faster and more efficient verification across software and hardware… Read More

How Synopsys Enables Gen AI on the Edge

Artificial intelligence and machine learning have undergone incredible changes over the past decade or so. We’ve witnessed the rise of convolutional neural networks and recurrent neural networks. More recently, the rise of generative AI and transformers. At every step, accuracy has been improved as depicted in the graphic… Read More

What is Different About Synopsys’ Comprehensive, Scalable Solution for Fast Heterogeneous Integration

Multi-die design has become the center of a lot of conversation lately. The ability to integrate multiple heterogeneous devices into a single package has changed the semiconductor landscape, permanently. This technology has opened a path for continued Moore’s Law scaling at the system level. What comes next will truly be exciting.… Read More

Will 50% of New High Performance Computing (HPC) Chip Designs be Multi-Die in 2025?

Predictions in technology adoption often hinge on a delicate balance between technical feasibility and market dynamics. While business considerations play a pivotal role, the technical category reasons for the success or failure of a prediction are more tangible and often easier to identify—if scrutinized with care. However,… Read More

A Deep Dive into SoC Performance Analysis: Optimizing SoC Design Performance Via Hardware-Assisted Verification Platforms

Part 2 of 2 – Performance Validation Across Hardware Blocks and Firmware in SoC Designs

Part 2 explores the performance validation process across hardware blocks and firmware in System-on-Chip (SoC) designs, emphasizing the critical role of Hardware-Assisted Verification (HAV) platforms. It outlines the validation workflow… Read More

A Deep Dive into SoC Performance Analysis: What, Why, and How

Part 1 of 2 – Essential Performance Metrics to Validate SoC Performance Analysis

Part 1 provides an overview of the key performance metrics across three foundational blocks of System-on-Chip (SoC) designs that are vital for success in the rapidly evolving semiconductor industry and presents a holistic approach to optimize… Read More