Since Aart de Geus, co-CEO and co-founder of Synopsys, gave his keynote at the Synopsys User Group (SNUG) conference in Silicon Valley last March, I’ve been hearing a lot more about the “Shift Left” in semiconductor design. Although I couldn’t attend Synopsys’ 25[SUP]th[/SUP]SNUG, I found some short videos on the Synopsys website… Read More

TCAD Enables Moore’s Law to Continue

We live in very interesting times, you can wear an Android watch from Samsung that uses 14 nm FinFET technology, attend the 52nd DAC conference in June to learn about EDA and IP vendors supporting FinFET, and read about research work for new devices down to 5 nm. TCAD is that critical software technology that enables the development… Read More

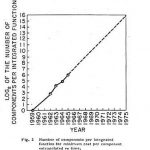

25 Years of SNUG; 50 Years of Moore’s Law

Earlier this week it was the Synopsys user group meeting SNUG. Not just any old SNUG but the 25th Annual SNUG. The first one was 15th March 1991 and was attended by 100 people. At the time, Synopsys had annual revenues of $22M. This year, the various SNUGs around the world will have a total attendance of 10,000 people and Synopsys revenue… Read More

Innovative MIPI Display Solution for UHD Mobile Devices

Today an SoC cannot be without multiple IP blocks integrated together in the most optimal manner. In such an environment, it’s natural that interoperability and configurability of an IP get prime considerations to achieve the best PPA (Power, Performance and Area) for the SoC containing that IP. While PPA is a basic criterion … Read More

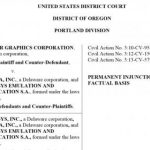

Wow: Synopsys v. Mentor Update!

As a reminder, the Synopsys v. Mentor drama started when Synopsys filed a Complaint for Declaratory and Injunctive Relief on the same day (September 27, 2012) as they entered into an agreement to acquire emulation provider EVE (ZeBu emulator systems), which competes with Mentor’s Veloce family of emulators. Apparently, upon… Read More

Shifting Chip Design Left!

In the traditional sense “Shift Left” is the process of making things simpler in an effort to make things faster. Shift Left was the theme of theDVCon keynote last week delivered by Synopsys co-founder and co-CEO Aart de Geus which is right on topic when it comes to modern semiconductor design and manufacturing, absolutely.

KEYNOTE:… Read More

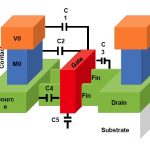

FinFET Design Enablement

We read about FinFET technology in the semiconductor press daily now, thanks to Intel introducing their TriGate transistors starting in 2011 and creating a race with foundries and IDMs to switch from planar CMOS nodes. To get some perspective about the progress of FinFET IP and EDA tools I spoke with two experts from Synopsys, Swami… Read More

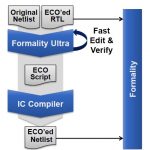

Faster ECOs Using Formal Analysis

Your latest SoC has just begun the tape-out process and then marketing comes back with a small update to the specification to make your design more competitive, or maybe your regression tests just found a minor bug in a single IP block that needs to be fixed. Should you go back in your design flow, change the RTL source code and then completely… Read More

Synopsys Earnings Call Q1 2015

Synopsys announced their results yesterday. Their 2014 already ended, this is the end of their fiscal first quarter. On the call were Aart, one of Synopsys’s two co-CEOs, the other being Chi-Foon Chan; and Trac Pham, the new CFO on his first earnings call.

Synopsys’s results were good. A quick look at the results. Revenue was $542M… Read More

Do You Need a Silicon Catalyst?

Lately there has been significant concern over the rising costs of designing in silicon and the troubling decline in venture investments in semiconductors. These alarming trends include fewer IPOs, a falloff in the amount and frequency of early stage seed investments, and comparatively low industry organic growth rates. A … Read More