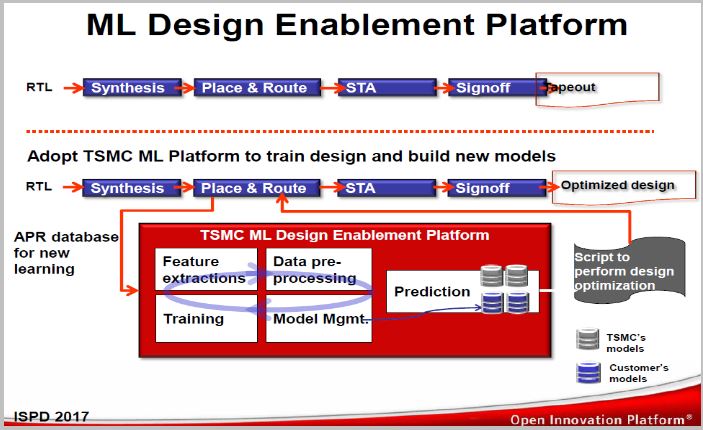

Recently we have been swamped by news of Artificial Intelligence applications in hardware and software by the increased adoption of Machine Learning (ML) and the shift of electronic industry towards IoT and automobiles. While plenty of discussions have covered the progress of embedded intelligence in product roll-outs, an… Read More

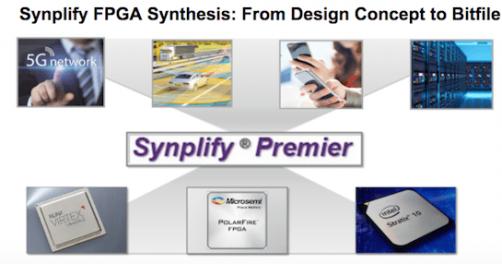

Webinar: Optimizing QoR for FPGA Design

You might wonder why, in FPGA design, you would go beyond simply using the design tools provided by the FPGA vendor (e.g. Xilinx, Intel/Altera and Microsemi). After all, they know their hardware platform better than anyone else, and they’re pretty good at design software too. But there’s one thing none of these providers want to… Read More

An Informal Update

I mentioned back in June that Synopsys had launched a blog on formal verification, intended to demystify the field and provide help in understanding key concepts. It’s been a few months, time to check in on some of their more recent posts.

First up, it feels like they are finding their groove. Relaxed style, useful topics but now with… Read More

How to Avoid Jeopardizing SoC Security when Implementing eSIM?

Smart card business is now more than 25 years old, we can assess that the semiconductor industry is able to protect the chips used for smart card or SIM application with a very good level (unfortunately, it’s very difficult to get access to the fraud percentage linked with smart cards, as bankers really don’t like to communicate on… Read More

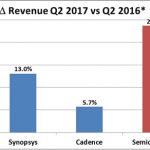

Semiconductor and EDA 2017 Update!

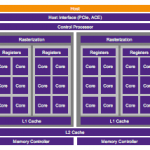

It really is an exciting time in semiconductors. The benchmarks on the new Apple A11 SoC and the Nvidia GPU are simply amazing. Even though Moore’s Law is slowing, the resulting chips are improving well above and beyond expectations, absolutely.

As I have mentioned before, non-traditional chip companies such as Apple, Amazon,… Read More

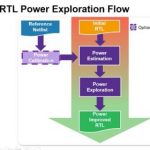

Clock Gating Optimization

You can save a lot of power in a design by gating clocks. For much of the time in a complex multi-function design, many (often most) of the clocks are toggling registers whose input values aren’t changing. Which means that those toggles are changing nothing functionally yet they are still burning power. Why not turn off those clock… Read More

Breakfast with Aart de Geus and the Foundries!

Being the number one EDA and the number one IP company does have its advantages and the resulting foundry relationships are a clear example. One of the DAC traditions that I truly enjoy is the Synopsys foundry breakfasts. Not only does Synopsys welcome scribes, they reserve a table up front for us and Synopsys CEO Aart de Geus has been… Read More

Samsung, Synopsys and Qualcomm at DAC

I’m a user of many Samsung products as my family has Samsung Galaxy smart phones and my MacBook Pro uses Samsung SSD for storage, so at DAC I attended a breakfast panel with presenters from Samsung, Synopsys and Qualcomm. This was the second day of DAC and they served us breakfast, and with the big names on the panel the room was… Read More

A Functional Safety Primer for FPGA – the White Paper

Following up on their webinar on functional safety in FPGA-based designs, Synopsys have now published a white paper expanding on some of those topics. For those who didn’t get a chance to see the webinar this blog follows the white paper flow and is similar but not identical to my webinar blog, particularly around differences between… Read More

Prototyping GPUs, Step by Step

FPGA-based prototyping has provided a major advance in verification and validation for complex hardware/software systems but even its most fervent proponents would admit that setup is not exactly push-button. It’s not uncommon to hear of weeks to setup a prototype or of the prototype finally being ready after you tape-out. … Read More