Ethernet’s continual adaptation to meet the demands of a data-rich, interconnected world can be credited to the two axes along which its evolution has been propelled. The first axis emphasizes Ethernet’s role in enabling precise and reliable control over interconnected systems. As industries embrace automation… Read More

AMD Puts Synopsys AI Verification Tools to the Test

The various algorithms that comprise artificial intelligence (AI) are finding their way into the chip design flow. What is driving a lot of this work is the complexity explosion of new chip designs required to accelerate advanced AI algorithms. It turns out AI is both the problem and the solution in this case. AI can be used to cut … Read More

Next-Gen AI Engine for Intelligent Vision Applications

Artificial Intelligence (AI) has witnessed explosive growth in applications across various industries, ranging from autonomous vehicles and natural language processing to computer vision and robotics. The AI embedded semiconductor market is projected to reach $800 billion by year 2030. Compare this with just $48 billion… Read More

VC Formal Enabled QED Proofs on a RISC-V Core

The Synopsys VC Formal group have a real talent for finding industry speakers to talk on illuminating outside-the-box-topics in formal verification. Not too long ago I covered an Intel talk of this kind. A recent webinar highlighted use of formal methods used together with a cool technique I have covered elsewhere called Quick… Read More

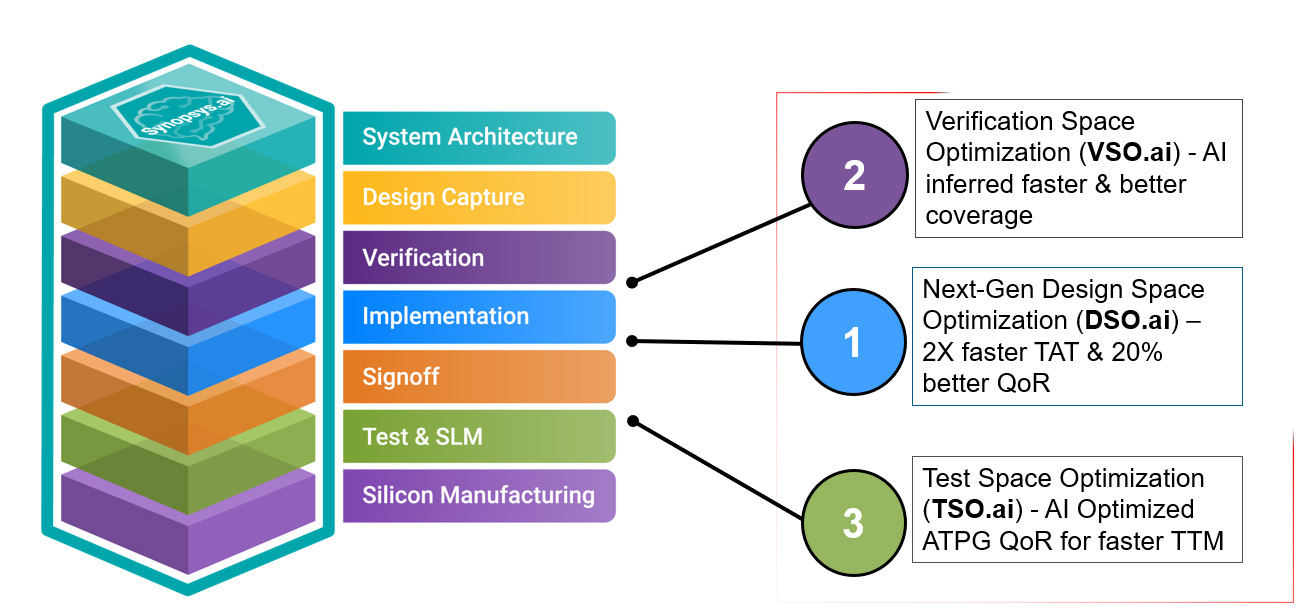

WEBINAR: Leap Ahead of the Competition with AI-Driven EDA Technology

The demands on today’s designs are relentless. Each generation of devices needs to be faster, smaller, more functional, more connected and more secure than the previous generation. In the face of all this, the time required for next-generation devices to hit the market is dramatically shrinking. That means the competitive landscape… Read More

Computational Imaging Craves System-Level Design and Simulation Tools to Leverage AI in Embedded Vision

Aberration-free optics are bulky and expensive. Thanks to high-performance AI-enabled processors and GPUs with abundant processing capabilities, image quality nowadays relies more on high computing power tied to miniaturized optics and sensors. Computational imaging is the new trend in imaging and relies on the fusion … Read More

Is Your RTL and Netlist Ready for DFT?

I recall an early custom IC designed at Wang Labs in the 1980s without any DFT logic like scan chains, then I was confronted by Prabhu Goel about the merits of DFT, and so my journey on DFT began in earnest. I learned about ATPG at Silicon Compilers and Viewlogic, then observability at CrossCheck where I met Jennifer Scher, now she’s… Read More

Synopsys Expands Agreement with Samsung Foundry to Increase IP Footprint

Many credible market analysis firms are predicting the semiconductor market to reach the trillion dollar mark over the next six years or so. Just compare this to the more than six decades it took for the market to cross the $500 billion mark. The projected growth rate is incredible indeed and is driven by fast growing market segments… Read More

Requirements for Multi-Die System Success

Chiplets continue to be a hot topic on SemiWiki, conferences, white papers, webinars and one of the most active chiplet enabling vendors we work with is Synopsys. Synopsys is the #1 EDA and #1 IP company so that makes complete sense.

As you may have read, I moderated a panel on Chiplets at the last SNUG which we continue to write about.

An Automated Method to Ensure Designs Are Failure-Proof in the Field

I don’t know about you, but when I think of mission-critical applications, I immediately think of space exploration or military operations. But in today’s world, mission-critical applications are all around us. Think about the cloud and how data is managed, analyzed, and shared to execute any number of tasks that have safety … Read More