During DVCon I met with Steve Bailey to get an update on Mentor’s verification. They were also announcing some new capabilities. I also attended Wally Rhines keynote (primarily about verification of course, since this was DVCon; I blogged about that here) and the Mentor lunch (it was pretty much Mentor all day for me) on the… Read More

Wally Rhines: Name That Graph!

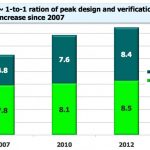

Wally Rhines gave the keynote at DVCon yesterday. He started out with a game of “name that graph” which was unfortunately a bit spoiled since when the names were revealed the first line was off the top of the screen. But he extrapolated several trends such as the decreasing number of fabs (the current trend is that there… Read More

How Can You Work Better with Your Foundry?

The fabless revolution in the digital semiconductor industry is no more, with just a few integrated device manufacturers (IDMs) remaining on the playing field, it is now the normal way to do business. However, the learning curve for each new process node continues as it always has, with a host of new technical challenges for the … Read More

SPICE Circuit Simulation at STMicroelectronics

At the 2010 DACI moderated a panel session on SPICE and Fast SPICE circuit simulation, and one of the panelists was PierLuigi Dagliofrom STMicroelectronics. To get an update on SPICE circuit simulation at ST I read a PDF document at Mentor titled: Improving the Quality of SPICE Simulation Results with Eldo Premier at ST.

ST does … Read More

SHIELDing the Android GPU developer in C

Repeat after me: SoCs are paperweights if they can’t be programmed. Succeeding with a new part today means supporting a robust developer program to attract and engage as many creatives as possible. NVIDIA has teamed up with Mentor Graphics in just such an adventure. If you read just the press release, you may have missed the real … Read More

Mentor Shines at DVCon

Mentor Graphics will be all over DVCon next week (February 25-28) at the DoubleTree hotel in San Jose.

In addition to attending all the panels, tutorials, posters, and the keynote, you can visit Mentor in booth 901 on the exhibit floor.

Here’s the lineup of Mentor-related events:… Read More

Magic? No! It’s Computational Lithography

The industry plans to use 193nm light at the 20nm, 14nm, and 10nm nodes. Amazing, no? There is no magic wand; scientists have been hard at work developing computational lithography techniques that can pull one more rabbit out of the optical lithography hat.

Tortured metaphors aside, the goal for the post-tapeout flow is the same… Read More

Notes from Common Platform: Collaborate or Die

FinFETs are hot, carbon nanotubes are cool, and collaboration is the key to continued semiconductor scaling. These were the main messages at the 2013 Common Platform Technology Forum in Santa Clara.

The collaboration message ran through most presenations, like the afternoon talk by Subi Kengeri of GLOBALFOUNDRIES and Joe Sawicki… Read More

Mentor Snags Two Awards at DesignCon

Oh, awards season! The glitz! The glamour! The most important and innovative new design products!

That last part is a key feature of the annual DesignVision awards and the Best in Test awards presented at DesignCon 2013. Mentor Graphics’ test products scored two wins: a DesignVision award for their new Tessent IJTAG product, and… Read More

Get the Latest Info on DFM at the SPIE Litho Conference

While the SPIE Advanced Lithography conference is best known for IC manufacturing, computational lithography, mask preparation and other back-end topics, there is also a significant amount of interest in Design for Manufacturing (DFM) at the conference because some litho issues are best (or only) addressed by modifying the… Read More