I was at EDPS in Monterey the last couple of days. It is one of the most interesting conferences to attend. Go next year since you already missed it this year. It is not big but the quality of the content is high. Historically the dinner in the middle is in the Monterey Yacht Club and there is a keynote speech. A few years ago it was me but this… Read More

Show Me How To Get Better DRC and LVS Results For My SoC Design

Most IC engineers learn best by hands-on experience when another more experienced person can show us what to do. If you cannot find that experienced person, then the next best thing is a video from an expert. I was surprised to find out that video was so important today that the #2 most viewed web site on the Internet was www.youtube.com… Read More

Sketch Router and auto-assist PCB layout

Archaic tech metaphors abound, stuck in the psyche of users everywhere. We still “dial” numbers, long after the benefit of a short pull area code disappeared. (Humans could dial 1, 2, or 3 a lot faster on a rotary phone, and there were fewer dialpulses for central office switches to decode – thus big cities with more phone traffic like… Read More

Mentor Acquires BDA!

Mentor Graphics acquired Berkeley Design Automation this morning. The details of the deal were unannounced. This is a strong move by Mentor to challenge Cadence and Synopsys in the nanometer analog/mixed-signal market and nanometer memory characterization market, respectively. Mentor not only acquires the technology and… Read More

Mentor U2U Is On April 10th

If you are a Mentor user, U2U, the Mentor User group is coming up on April 10th. This is an all day event at the DoubleTree. The event is free. Registration starts at 8am and the agenda itself starts at 9am. There is a reception from 5-6pm in the evening.

There are three keynotes. At 9am: Wally Rhines, CEO of Mentor. The Big Squeeze. For … Read More

A Fill Solution for 20nm at TSMC

By Jeff Wilson, Mentor Graphics

We’ve talked about the new requirements for Fill in IC design for advanced nodes in previous blogs on this site. This time I’d like describe the fill solution that Mentor and TSMC have jointly developed to meet the requirements of fill for TSMC’s 20nm (N20) manufacturing process.

The traditional… Read More

Dr. Walden Rhines Vision on Semiconductor & India

Last month India Electronics & Semiconductor Association (IESA) held its Vision Summit at Bangalore in which luminaries from across the semiconductor and electronics industry presented their views about the future of this industry and India’s progress. Dr. Walden C. Rhines, Chairman and CEO of Mentor Graphicspresented… Read More

One SPIE session not to miss

The time is nigh for another meeting of the practitioners of the lithographic arts, dark and otherwise, at the SPIE Advanced Lithography symposium.

I love this conference for the engagement you see, both in the sessions and in the hallways. People actually meet and talk and argue. There’s always interesting gossip, exciting technologies,… Read More

Verification of Power Delivery Networks

Power delivery networks (PDN) are the metal structures on a chip that delivers the power. In a high-end desktop SoC this might be delivering as much as 150W, and with voltages around 1V that means over 150 amps of current. Clearly getting the PDN correct is critical for a correctly functioning chip. One of the challenges to verifying… Read More

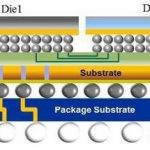

Smart Strategies for Efficient Testing of 3D-ICs

3D-IC has a stack of dies connected and packaged together, and therefore needs new testing strategies other than testing a single die. It’s given that a single defective die can render the whole of 3D-IC unusable, so each die in the stack must be completely and perfectly tested before its entry into that stack. Looking at it from a … Read More