When it comes to safety and automotive systems, ISO 26262 is the standard by which system vendors are judged. As with all things the devil is in the details. To be compliant to the standard, design teams must have a well-defined and rigorous design and validation process in place that copiously documents all the requirements of their… Read More

Emulation Methodology for Drones and Other Video-Intensive Multimedia SoCs

What do drones, augmented reality devices, and 4K UHD TV have in common? They all include complex system-on-chips (SoCs) that must encode and decode, in real-time, data for increasingly higher definition video content. Verifying that these SoC designs are functionally correct is quite complex, but they must also function efficiently… Read More

Verification Trends: 2016

Periodically Mentor does us all a big favor by commissioning a survey of verification engineers across the world to illuminate trends in verification. This is valuable not only to satisfy our intellectual curiosity but also to help convince managers and finance mandarins that our enthusiasm to invest in new methods and tools … Read More

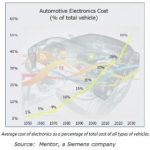

Walden Rhines on the Automotive Electronics Landscape

Mentor President and CEO Walden Rhines gave a comprehensive overview of the automotive electronics landscape at the Mentor Integrated Electrical Solutions Forum (IESF) in Plymouth, Mich., this week. A key focal point of Rhines’ comments was the twin industry disruptors: EVs and AVs.

A Texas Instruments alum, Rhines described… Read More

High-Level Synthesis for Automotive SoCs

Some of the world’s most complex Systems-on-Chip (SoCs) are being developed for automotive applications. These SoCs have heterogeneous architectures with a variety of processors and accelerators that do real-time image processing for assisted and autonomous driving applications. The Bosch Visiontec team, in Sophia Antipolis,… Read More

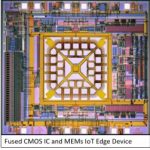

Fusing CMOS IC and MEMS Design for IoT Edge Devices

In my 34 years in IC and EDA, it never ceases to amaze me as to how ingenious designers can be with what is given them. Mentor, a Siemens business, has released a wonderful white paper that is proof of this yet again. The white paper steps through how one of their customers, MEMSIC, used the Tanner tool suite to develop a combination CMOS… Read More

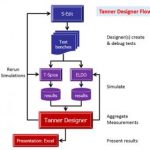

Project Management Tools for Analog IP Verification

Large SoC design teams typically have a cadre of project managers to oversee all facets of functional verification — e.g., specification, reviews, directed testbench development, automated (pseudorandom) testcase generation, HDL coverage measurement and reporting, and bug identification/tracking database management.… Read More

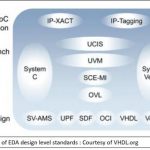

Why Open and Supported Interfaces Matter

Back in the early 1980’s during the nascent years of electronic design automation (EDA), I worked at Texas Instruments supporting what would become their merchant ASIC business. Back then, life was a bit different. The challenge we faced was to make our ASIC library available on as many EDA flows as we could to give as many users as… Read More

Automotive IC Design Requires a Unique EDA Tool Emphasis

Semiwiki readers are no doubt very familiar with the increasing impact of the automotive market on the semiconductor industry. The magnitude and complexity of the electronic systems that will be integrated into upcoming vehicle designs reflects the driver automation, safety, and entertainment features that are in growing… Read More

Whitepaper : The True Costs of Process Node Migration

Mentor, A Siemens Business, just released a new white paper entitled, “The True Costs of Process Node Migration” written by John Ferguson. This is a good quick read that highlights some of the key areas that are often over looked when contemplating a shift of process nodes for your next design.

When considering a shift to a more advanced… Read More