Being new in Ottawa and trying to get some momentum towards automation in full custom layout I was telling industry people that I am interested to work with everybody to move this agenda forward. My Director of Engineering at that time, Peter Gillingham, took me to visit Carleton University in Ottawa. One of his professor friends,… Read More

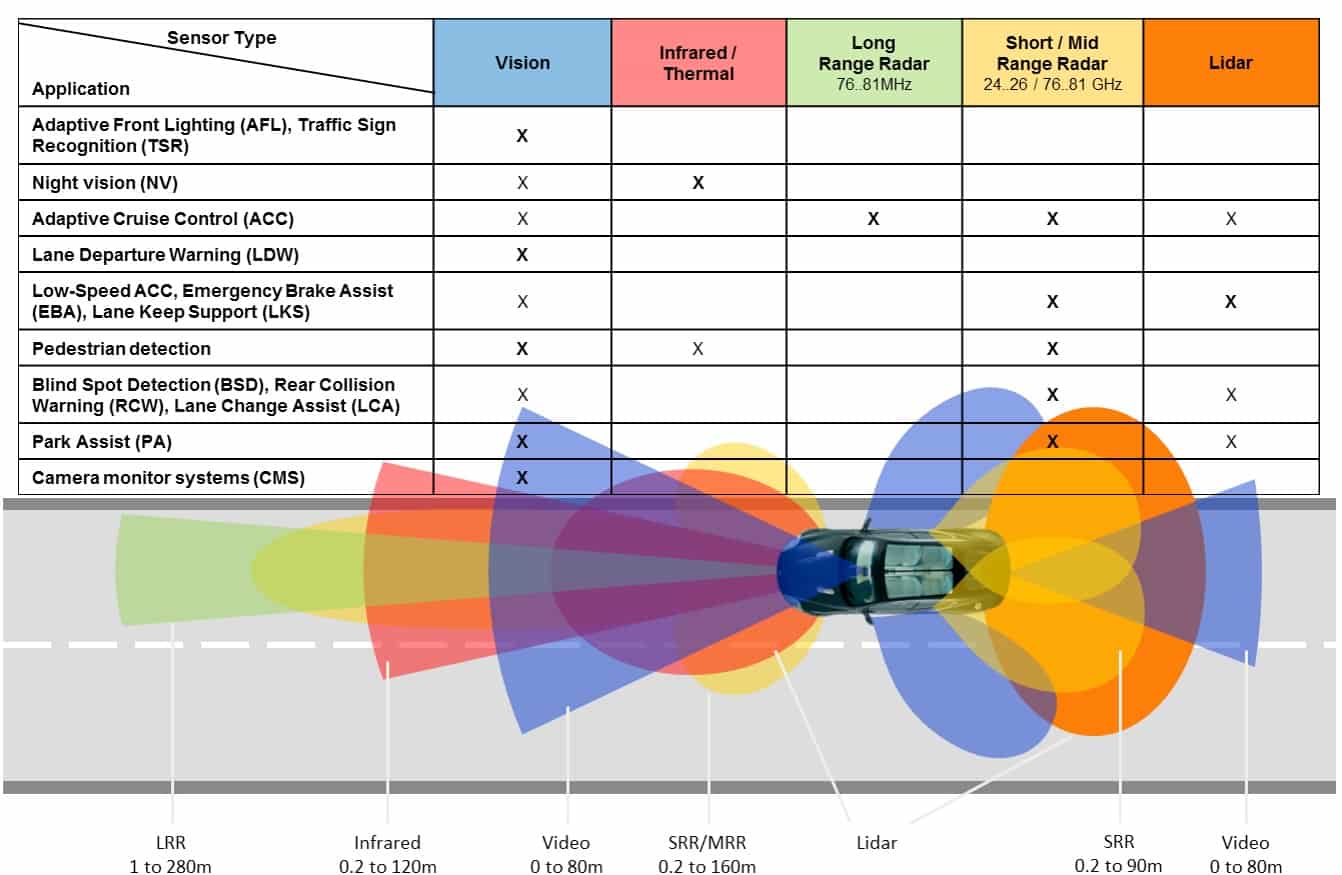

Autonomous Vehicles Upending Automotive Design Process

The automotive industry has a history of bringing about disruptive technological advances. One only needs to look at the invention of the assembly line by Henry Ford to understand the origins of this phenomenon. Today we stand on the brink of a massive change in how cars operate and consequently how they are built. A number of automotive… Read More

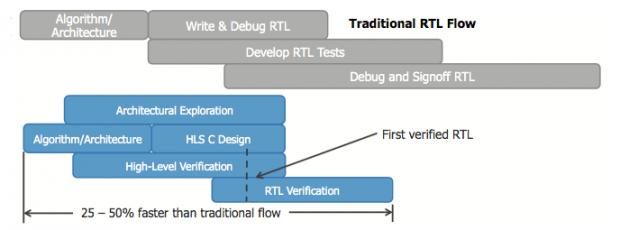

HLS Rising

No-one could accuse Badru Agarwala, GM of the Mentor/Siemens Calypto Division, of being tentative about high-level synthesis. (HLS). Then again, he and a few others around the industry have been selling this story for quite a while, apparently to a small and not always attentive audience. But times seem to be changing. I’ve written… Read More

Test Compression for Mission Critical SoCs

With the advent of the Internet-of-Things (IoT), Industry 4.0, Cognitive Computing, and autonomous vehicles and robots we are seeing an unprecedented number of systems-on-a-chip (SoCs) going into mission-critical applications. To accomplish the complexity of these applications, SoCs are being manufactured in leading-edge… Read More

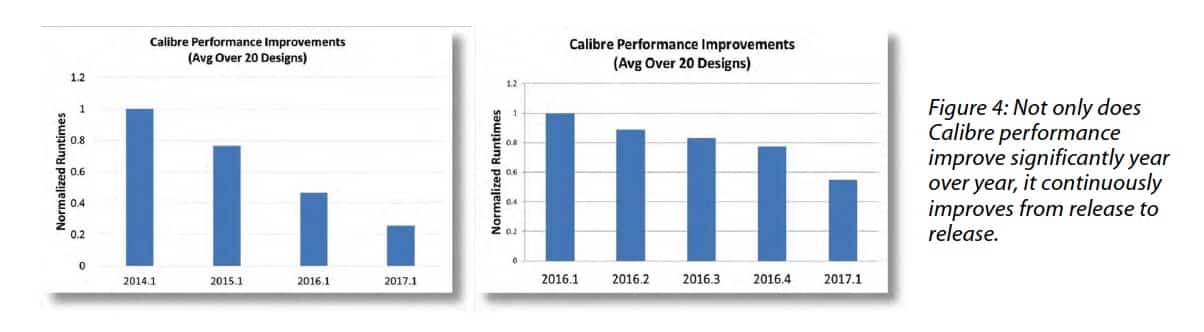

High Calibre Development Keeps Mentor on Top of the Game

One might be tempted to think that technology driven gains in computer performance might be enough to keep up with the needs of design and verification tools. We know that design complexity is increasing at a rate predicted by Moore’s Law. We also know that the performance of the computers used during IC development benefit from … Read More

Mentor FINALLY Acquires Solido Design

I say finally because it was a long time coming… almost ten years to be exact. I started doing business development work for both Solido and Berkeley Design Automation about ten years ago and have been trying to put them together ever since. The synergy was obvious, like peanut butter and jelly. In fact, this is my third time … Read More

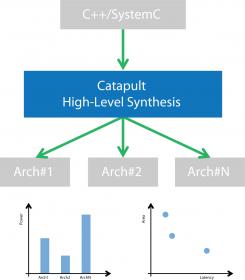

High-Level Design for Automotive Applications

Automotive markets have added pressure on semiconductor/systems design through demand for ISO26262 compliance – this we all know. But they have also changed the mix of important design types. Once class of design that has become very significant in ADAS, and ultimately autonomous applications, is image signal processing (ISP).… Read More

Electronic Design for Self-Driving Cars Center-Stage at DVCon India

The fourth installment of DVCon India took place in Bangalore, September 14-15. As customary, it was hosted in the Leela Palace, a luxurious and tranquil resort in the center of Bangalore, and an excellent venue to host the popular event.

As reported in my previous DVCon India trip reports, the daily and evening traffic in Bangalore… Read More

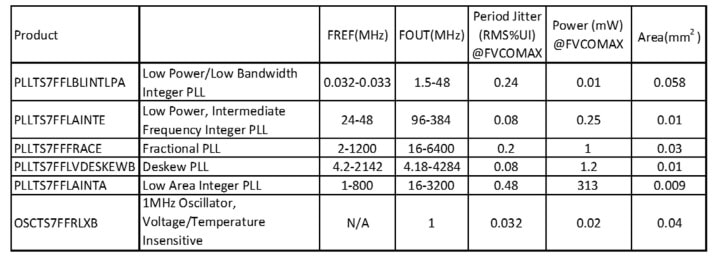

Silicon Creations talks about 7nm IP Verification for AMS Circuits

Designing at 7nm is a big deal because of the costs to make masks and then produce silicon that yields at an acceptable level, and Silicon Creations is one company that has the experience in designing AMS IP like: PLL, Serializer-Deserializer, IOs, Oscillators. Why design at 7nm? Lots of reasons – lower power, higher speeds,… Read More

ARM TechCon 2017 Preview with Mentor!

Next week is ARM TechCon which is one of my favorite conferences (SemiWiki is an event partner). This year is lucky number thirteen for ARM TechCon and it includes more than sixty hours of sessions plus more than one hundred ARM partners in the exposition. I will be signing free copies of our new book “Custom SoCs for IoT: Simplified”… Read More