Monday at DAC this year started off on a very optimistic note as Joe Sawicki from Siemens EDA presented in the Pavilion on the topic of Digitalization, a frequent theme in the popular press because of the whole Work From Home transition that we’ve gone through during the pandemic. Several industries are benefiting from the… Read More

System Technology Co-Optimization (STCO)

My first exposure to seeing multiple die inside of a single package in order to get greater storage was way back in 1978 at Intel, when they combined two 4K bit DRAM die in one package, creating an 8K DRAM chip, called the 2109. Even Apple used two 16K bit DRAM chips from Mostek to form a 32K bit DRAM, included in the Apple III computer, circa… Read More

Siemens EDA will be returning to DAC this year as a Platinum Sponsor.

The 38th Design Automation Conference is next week and this one is for the record books. Having been virtual the last two years, next week we will meet live once again. I think we may have all taken for granted the value of live events but now we know how important they are on both a professional and human level, absolutely.

“The… Read More

Machine Learning Applied to IP Validation, Running on AWS Graviton2

I recall meeting with Solido at DAC back in 2009, learning about their Variation Designer tool that allowed circuit designers to quickly find out how their designs performed under the effects of process variation, in effect finding the true corners of the process. Under the hood the Solido tool was using Machine Learning (ML) techniques… Read More

Siemens EDA Automotive Insights, for Analysts

There is a classical approach to EDA marketing, and semiconductor marketing at times, which aims exclusively at technical customers and the businesspeople immediately around those experts. The style is understandable and necessary. Those folks are the direct influencers and buyers of the products we are promoting, so we must… Read More

Tessent Streaming Scan Network Brings Hierarchical Scan Test into the Modern Age

Remember when you had to use dial up internet or parallel printer cables connected directly to the printer to print something? Well even if you don’t remember these things, you know that now there is a better way. Regrettably, the prevalent methods used for hierarchical Design for Test (DFT) still look at lot like this – SoC level … Read More

Minimizing MCU Supply Chain Grief

I doubt there is anyone who hasn’t felt the impact of supply chain problems, from late ecommerce deliveries (weeks) to kitchen appliances (up to 6 months or more). Perhaps no industry has been more affected than auto makers, whose cars are now critically dependent on advanced electronics. According to a white paper recently released… Read More

Back to Basics in RTL Design Quality

Harry Foster waxes philosophical in a recent white paper from Siemens EDA, in this case on the origins of bugs and the best way to avoid them. Spoiler alert, the answer is not to make them in the first place or at least to flush them out very quickly. I’m not being cynical – that really is the answer though practice often falls short of ideal.… Read More

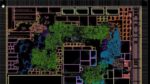

APR Tool Gets a Speed Boost and Uses Less RAM

Automatic Place and Route (APR) tools have been around since the 1980s for IC design teams to use, and before that routing was done manually by very patient layout designers. Initially the big IDMs had their own internal CAD groups coding APR tools in house, but eventually the commercial EDA market picked up this automation area,… Read More

DARPA Toolbox Initiative Boosts Design Productivity

When you think of the Defense Advanced Research Projects Agency (DARPA), this first thing that comes to mind is the development of the internet. And indeed, if you look at their website’s historic timeline, the development of ARPANET, as it was known at the time, is shown prominently in 1969. Incidentally, I actually used one of … Read More