This has got to be one of the most interesting and disruptive EDA acquisitions I have seen in some time. Another one that comes to mind is Siemens acquiring Mentor Graphics. We have been covering EDA PLM companies since the start of SemiWiki and have worked with most of them. If I had to keep score I would say it’s about even but … Read More

What’s At the Center of Your SoC Design Process?

I love starting a new project from scratch, because there’s that optimistic feeling of having no constraints and being able to creatively express myself and get the job done right this time. For SoC designs today there are teams of engineers and maybe a program manager plus a marketing person that define the features, budget… Read More

SEMI Takes the Jim Hogan and Simon Butler Conversation Virtual

As I originally reported a few weeks ago, the Jim Hogan fireside chat with Methodic’s CEO and founder Simon Butler was moved to a virtual event on May 1. The event was produced by the Electronic System Design (ESD) Alliance, a SEMI Strategic Technology Community. Bob Smith, executive director of ESDA, moderated the event. I am happy… Read More

Project-Centric Design Process, or IP-centric

How do most IC design teams organize their work during the design process?

Most design teams would say that they organize their work into a project-centric view, and that at the beginning of the process use a tool for requirements management, maybe a bug tracker, or some design management tool. On the four IC designs that I worked … Read More

UPDATE: Everybody Loves a Winner

Building a successful startup is hard, very hard. Creating a new category along the way is even more difficult. Those that succeed at both endeavors are quite rare. This is why an upcoming ESD Alliance event is a must-see in my view. The event is entitled “Jim Hogan and Methodics’ Simon Butler on Bootstrapping a Startup to Profitability… Read More

Avoiding Fines for Semiconductor IP Leakage

In my semiconductor and EDA travels I’ve enjoyed visiting engineers across the USA, Canada, Europe, Japan, Taiwan and South Korea. I’ll never forget on one trip to South Korea where I was visiting a semiconductor company and upon reaching the lobby a security officer asked me to take out my laptop computer, because he wanted me to… Read More

Webinar Recap: IP Security Threats in your SoC

Three years ago my youngest son purchased a $17 smart watch on eBay, but then my oldest son read an article warning about how that watch would sync with your phone, then send all of your contact info to an address in China. My youngest son then wisely turned the watch off, and never used it again. Hackers have been able to spoof and hide … Read More

WEBINAR: Generating and Measuring IP Security Threat Levels For Your SoCs

IPs have an attack surface that indicates how they can be compromised in real world scenarios. Some portions of the attack surfaces are well known, others are discovered during analysis, testing or out in the field. SoCs that use large collections of IPs need a systematic and reliable way to determine the various security vulnerabilities… Read More

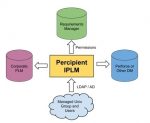

Workflow Automation Applied to IP Lifecycle Management

I often blog about a specific EDA tool, or an IP block, but the way that SoC design teams approach their designs and then use tools and IP can either be a manual, ad-hoc process, or part of something that is well-documented, following a design methodology. Back in the 1980’s while at Intel our team first created a design methodology… Read More

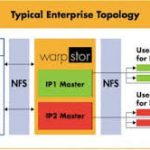

WEBINAR: Lightspeed Data Sync – Design Workspace Problems Solved!

With every process node and every SOC design, engineering and IT teams are experiencing an unprecedented data explosion. User workspaces routinely exceed 10’s of GB and sometimes even 100’s of GB. Regression runs, characterization runs, design and debug of workspaces, building verification environments – all of these… Read More