Harry Foster is Chief Scientist in Verification at Siemens EDA and has held roles in the DAC Executive Committee over multiple years. He gave a lunchtime talk at DVCon on the verification complexity topic. He is an accomplished speaker and always has a lot of interesting data to share, especially his takeaways from the Wilson Research… Read More

Electronic Design Automation

Taking the Risk out of Developing Your Own RISC-V Processor with Fast, Architecture-Driven, PPA Optimization

Are you developing or thinking about developing your own RISC-V processor? You’re not alone. The use of the RISC-V ISA to develop processors for SoCs is a growing trend. RISC-V offers a lot of flexibility with the ability to customize or create ISA and microarchitectural extensions to differentiate your design no matter your application… Read More

Optimizing Return on Investment (ROI) of Emulator Resources

Modern day chips are increasingly complex with stringent quality requirements, very demanding performance requirement and very low power consumption requirement. Verification of these chips is very time consuming and accounts for approximately 70% of the simulation workload on EDA server farms. As software-based simulators… Read More

WEBINAR: Design Cost Reduction – How to track and predict server resources for complex chip design project?

During the design of complex chips, cost reduction is becoming a real challenge for small, medium and large companies. Resource management is a key to contain design cost.

The chip design market is expecting automated solutions to help in the resource prediction, planning and analysis. AI-based technologies are promising … Read More

Multiphysics Analysis from Chip to System

Multiphysics simulation is the process of computational methods to model and analyze a system to understand its response to different physical interactions like heat transfer, electromagnetic fields, and mechanical structures. Using this technique, designers can generate physics-based models and analyze the behavior… Read More

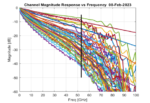

Feeding the Growing Hunger for Bandwidth with High-Speed Ethernet

The increasing demands for massive amounts of data are driving high-performance computing (HPC) to advance the pace in the High-speed Ethernet world. This in turn, is increasing the levels of complexity when designing networking SoCs like switches, retimers, and pluggable modules. This growth is accelerating the need for … Read More

Takeaways from SNUG 2023

Synopsys pulled out all the stops for this event. I attended the first full day, tightly scripted from Aart’s keynote kick off to 1×1 interviews with Synopsys executives to a fireside chat between Sassine Ghazi (President and COO) and Rob Aitken (ex-Fellow at Arm, now Distinguished Architect at Synopsys). That’s a lot of … Read More

AI in Verification – A Cadence Perspective

AI is everywhere or so it seems, though often promoted with insufficient detail to understand methods. I now look for substance, not trade secrets but how exactly they using AI. Matt Graham (Product Engineering Group Director at Cadence) gave a good and substantive tutorial pitch at DVCon, with real examples of goal-centric optimization… Read More

Mapping SysML to Hardware Architecture

The Systems Modeling Language (SysML) is used by systems engineers that want to specify, analyze, design, verify and validate a specific system. SysML started out as an open-source project, and it’s a subset of the Unified Modeling Language (UML). Mirabilis Design has a tool called VisualSim Architect that imports your… Read More

Full-Stack, AI-driven EDA Suite for Chipmakers

Semiconductor technology is among the most complex of technologies and the semiconductor industry is among the most demanding of industries. Yet the ecosystem has delivered incredible advances over the last six decades from which the world has benefitted tremendously. Yes, of course, the markets want that break-neck speed… Read More

Chemical Origins of Environmental Modifications to MOR Lithographic Chemistry