Ever since the cost of development started growing exponentially, engineering teams have been deploying a shift-left strategy to software development and system verification. While this has helped contain cost and accelerated product development schedules, a shift-left strategy is not without challenges. A virtual platform… Read More

Electronic Design Automation

5G and Aircraft Safety: Simulation is Key to Ensuring Passenger Safety

The new 5G C-band service is now up and running in the U.S., and subscribers are finally starting to see some of the promise of 5G. The new C-band services are primarily in spectrum allocations between 3 and 4 GHz, providing the wider channel allocation bandwidths necessary to deliver significantly higher data throughput. At the… Read More

Use Existing High Speed Interfaces for Silicon Test

The growth of complexity for silicon test as it relates to test data volume and test times is driven by multiple concurrent factors. One dimension is simply the increase in silicon complexity. However, other factors are playing a role as well. These include higher reliability requirements for new applications such as automotive,… Read More

5G Network Activation Update

As a pilot and semiconductor professional I was a bit shocked to get an Airworthiness Directive due to the 5G rollout. Airworthiness Directives are legally enforceable regulations issued by the FAA to correct an unsafe condition in a product:

“Airworthiness Directive (AD) 2021-23-12 was issued for all fleets in December… Read More

Getting to Faster Closure through AI/ML, DVCon Keynote

Manish Pandey, VP R&D and Fellow at Synopsys, gave the keynote this year. His thesis is that given the relentless growth of system complexity, now amplified by multi-chiplet systems, we must move the verification efficiency needle significantly. In this world we need more than incremental advances in performance. We need… Read More

Webinar: Beyond the Basics of IP-based Digital Design Management

According to the ESD Alliance, the single biggest revenue category in our industry is for semiconductor IP, so the concept of IP reuse is firmly established as a way to get complex products to market more quickly and reducing risk. On the flip side, with hundreds or even thousands of IP blocks in a complex SoC, how does a team, division… Read More

Prototype enables new synergy – how Artosyn helps their customers succeed

Artosyn Microelectronics, a leading provider of AI SoCs for drones and other sophisticated applications finds itself at the intersection of hardware architecture and software development. “Our customers are advancing the state of AI programming every day,” said Shen Sha, Senior R&D Manager of Artosyn’s AI Chip Department.… Read More

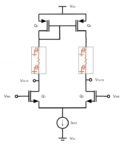

Analog IC Layout Automation Benefits

I viewed a recent webinar from Paul Clewes of Pulsic, and the topic was Balancing Analog Layout Parasitics in MOSFET Differential Pairs. This topic interests me, because back in 1982 I wrote my first IC layout automation tool at Intel that automatically created 15% of a GPU chip layout called the 82786, then joined Silicon Compilers… Read More

Non Volatile Memory IP is Invaluable for PMICs

Power Management ICs are a vitally important part of system design. Evidence of this is cited by a Synopsys white paper that mentions how Apple acquired a portion of PMIC developer Dialog Semiconductor that was previously their exclusive PMIC supplier. Clearly Apple had decided that PMIC design was a strategic differentiating… Read More

Using a GPU to Speed Up PCB Layout Editing

I can remember back in the 1980s how Apollo workstations were quite popular, because they accelerated the graphics display time for EDA tools much better than competitive hardware. Fast forward to 2022 and we have the same promise of speeding up EDA tools like PCB layout editing by using a GPU. At the 58th DAC there was a session called,… Read More

Making Intel Great Again!