Double patterning at 20nm is one of those big unavoidable changes that it is almost impossible to know too much about. Mentor’s David Abercrombie, DFM Program Manager for Calibre, has written a series of articles detailing the multifaceted impacts of double patterning on advanced node design and verification. There is… Read More

Electronic Design Automation

Apache/Ansys presents: 3DIC thermal, transmission lines, low frequency analysis

Late in January it is DesignCon at the Santa Clara convention center from January 28th-31st. Details are here.

On Tuesday from 11.05 to 11.45 Apache and Ansys will be presenting on Thermal Co-analysis of 3D IC/packages/system. This is being presented by a whole team of people: Stephen Pan, senior product specialist at ANSYS; Norman… Read More

Apache Presents: ESD analysis

The 26th Conference on VLSI Design will be in Pune, India from January 5th to 10th at the Hyatt Regency. Details on the conference here. Registration here. I happened to be involved in the first of these conferences, which was held in Edinburgh where I was wrapping up my PhD. It was in the considerably less palatial surroundings of … Read More

Schematic Capture and SPICE from Symica

At DAC in June I first blogged about Symicabecause they offered a Fast SPICE circuit simulator, and today I discovered a free version so I decided to write up a mini-review for you.… Read More

A Brief History of Synopsys

One of the largest software companies in the world, Synopsys is a market and technology leader in the development and sale of electronic design automation (EDA) tools and semiconductor intellectual property (IP). Synopsys is also a strong supporter of local education through the Synopsys Outreach Foundation. Each year in multiple… Read More

Happy Holidays

At times of this year, companies usually get their salespeople to submit the names and addresses of all their customers. They then get an expensive card printed and mail it out. What the recipient does is anyone’s guess, from throwing it straight in the bin to using it to decorate the office.

Atrenta decided to do something … Read More

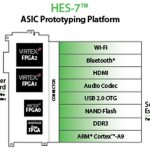

Zynq out of the box, in FPGA-based prototyping

Roaming around the hall at ARM TechCon 2012 left me with eight things of note, but one of the larger ideas showing up everywhere is the Xilinx Zynq. Designers are enthralled with the idea of a dual-core ARM Cortex-A9 closely coupled with programmable logic.… Read More

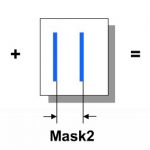

Double Patterning Verification

You can’t have failed to notice that 20nm is coming. There are a huge number of things that are different about 20nm from 28nm, but far and away the biggest is the need for double patterning. You probably know what this is by now, but just in case, here is a quick summary.

Lithography is done using 193nm light. Today we use immersion… Read More

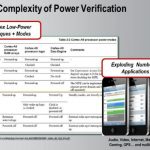

Apache Power Artist Capabilities II

This is the second part of my discussion with Paul Traynar, Apache’s PowerArtist guru. The first part discussed sequential reduction capabilities. Part I was here.

There are two big challenges with doing power analysis at the RTL level. Firstly, how do you get an accurate enough model of what the design will dissipate given… Read More

Subsystem IP, myth or reality?

I have participated to a panel during IP-SoC, I must say that “Subsystem IP, myth or Reality” was a great moment. The panel was a mix of mid-size IP vendor (CAST, Sonics), one large EDA (Martin Lund from Cadence), Semiwiki blogger and one large IDM (Peter Hirt from STM) who has very well represented the customer side. And, to make the… Read More

From the Selfie to Samantha: The Next Trillion-Dollar Behavior