Modern SoC (System On Chip) designs contain a larger number of RAM (Random Access Memory) instances, so how do you know what the speed, timing and power are for any instance? There are a couple of approaches:

[LIST=1]

Electronic Design Automation

Carbon has Six Weeks of ARM, not to Mention Imagination and MIPS

As George E.P. Box said, “essentially all models are wrong but some are useful.” That is certainly the case with Carbon’s models. For processors they have two models, one that is fast (but not timing-accurate) and one that is accurate (but not fast). But both are useful.

Carbon attended the ARM TechCon in Santa… Read More

ICCAD at 30: Alberto Looks Back and Forward

At ICCAD earlier this week, CEDA sponsored a talk by Alberto Sangiovanni-Vincentelli looking back over the last 30 years (it is the 30th anniversary of ICCAD) and looking to the future. As is always the case in these sorts of presentations, the retrospective contained a lot more detail than the going forward part. Clayton Christensen… Read More

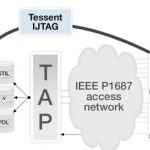

IJTAG, Testing Large SoCs

Test is the Rodney Dangerfield of EDA, it doesn’t get any respect. All designs need to be tested but somehow synthesis, routing, analog layout and the rest are the sexy areas. In my spoof all purpose EDA keynote address I even dissed it:You are short on time so slip in a quick mention of manufacturing test. Who knows anything … Read More

ARM adopting SpyGlass IP Kit, joining TSMC’s soft IP9000 Quality Assessment Program

More than one year old now, TSMC’s soft IP quality assessment program is a joint effort between TSMC and Atrenta to deploy a series of SpyGlass checks that create detailed reports of the completeness and robustness of soft IP. This soft IP quality program has been the first to be initiated by a Silicon foundry on other than “Hard IP”,… Read More

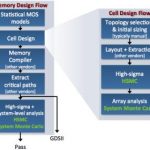

Solido and TSMC for 6-Sigma Memory Design

Solido Design Automation and TSMC recently published an article in EE Times describing how Solido’s High-Sigma Monte Carlo tool is used with TSMC PDK’s to achieve high-yield, high-performance memory design. This project has been a big part of my life for the past three years and it is time for a victory lap!

In TSMC 28nm, 20nm and … Read More

Embedding 100K probes in FPGA-based prototypes

As RTL designs in FPGA-based ASIC prototypes get bigger and bigger, the visibility into what is happening inside the IP is dropping at a frightening rate. Where designers once had several hundred observation probes per million gates, those same several hundred probes – or fewer if deeper signal captures are needed – are now spread… Read More

A Most Significant Man

Most of us live perfectly good lives without distinction, fame, or note. Others rack up the honors, filling their walls and resumes with recognition of their brilliance. Like Dr. Janusz Rajski.

Rajski is the director of engineering for the test products at Mentor Graphics, an IEEE Fellow, and the inventor of embedded deterministic… Read More

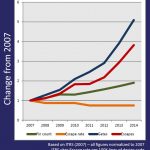

Gustafson on Parallel Algorithms

At the keynote for ICCAD this morning, John Gustafson of AMD (where he is Chief Graphics Product Architect as well as a Fellow) talked about parallel algorithms. Like Gene Amdahl, whose law states that parallel algorithms are limited by the part that cannot be parallelized (if 10% is serial, then even if the other part takes place… Read More

Chip On Wafer On Substrate (CoWoS)

Our EDA industry loves three letter acronyms so credit the same industry for creating a five letter acronym CoWoS. Two weeks ago TSMC announced tape-out of their first CoWoS test chip integrating with JEDEC Wide I/O mobile DRAM interface, making me interested enough to read more about it. At the recent TSMC Open Innovation Platform… Read More

Quantum Computing Technologies and Challenges