I won’t be able to attend Chris Rowen’s presentation here at the GlobalPress Electronic Summit since I’m going to the first day of the Linley Mobile Microprocessor conference. In fact I wonder if Chris himself will make it since he was running in the Boston marathon on Monday. He finished about 10 minutes before… Read More

Electronic Design Automation

Atrenta, Forte and Jasper LOVE DAC

I LOVE DAC is back. This year the sponsors are Atrenta, Jasper and Forte (hey, all semiwiki subscribers). The way it works is that you register on the DAC website here and you get a free three-day exhibit pass. In addition to everything going on in the exhibit hall, including the pavilion panels held there, the pass also gives access… Read More

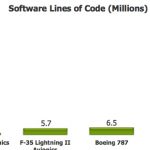

Wally Rhines: Embedded Software the Next Revolution?

As seems to be traditional, Wally Rhines gave a keynote here at the GlobalPress Electronics Summit here in sunny Santa Cruz. It was entitled Embedded Software, the Next Revolution in EDA. Unlike Cadence and Synopsys, Mentor has a strong position in embedded software. It has been build up over a long time through a series of acquisitions… Read More

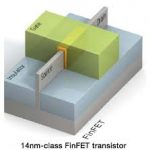

FinFETs: Ask the Experts II!

As I have mentioned 28 times already, on Friday (April 19[SUP]th[/SUP]) I will be keynoting FinFET day at the EDPS conference in Monterey. This is an excellent opportunity to ask the experts about the challenges of FinFET design and manufacturing in an intimate setting (60 people). If you are interested register today and use the… Read More

Webinar: Making a Simple, Structured and Efficient VHDL Testbench

Most simple testbenches have close to no structure, are terrible to modify and hopeless to understand. They often take far too much time to implement and provide close to no support when debugging potential problems. This webinar will demonstrate how to build a far better testbench with respect to all these issues – in significantly… Read More

Variation-aware IC Design

We’ve blogged before about Layout Dependent Effects (LDE) on SemiWiki and how it further complicates the IC design and layout process, especially at 28nm and lower nodes because the IC layout starts to change the MOS device performance. There’s an interesting webinarfrom Cadence on Variation-aware IC Design, … Read More

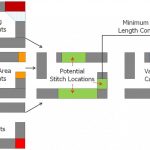

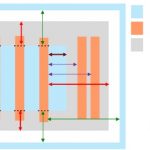

Chasing DP Rabbits

“Now, here, you see, it takes all the running you can do, to keep in the same place. If you want to get somewhere else, you must run at least twice as fast as that!”

—Lewis Carroll, Through the Looking Glass

The use of stitching can greatly reduce the number of double patterning (DP) decomposition violations that a designer has to resolve.… Read More

Two New TSMC-Cadence Webinars for Advanced Node Design

Foundries and EDA vendors are cooperating at increasing levels of technical intimacy as we head to the 20nm and lower nodes. Cadence has a strong position in the EDA tools used for IC design and layout of custom and AMS (Analog Mixed-Signal) designs. They have created a series of webinars to highlight the design challenges and new… Read More

FinFETs: Ask the Experts!

On Friday (April 19[SUP]th[/SUP]) I will be keynoting FinFET day at the EDPS conference in Monterey. This is an excellent opportunity to ask the experts about the challenges of FinFET design and manufacturing in an intimate setting (60 people). If you are interested register today and use the promo codeSemiWiki-EDPS-JFR and … Read More

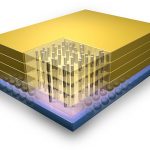

3D IC: Are We There Yet?

For the last few years, thru silicon via (TSV) based ICs have been looming in the mist of the future. Just how far ahead are they? Xiliinx famously has a high-end gate-array in production on a 2.5D interposer, Micron has a memory cube, TSMC has done various things in 3D that it calls CoWoS (chip on wafer on substrate), Qualcomm have been… Read More

From the Selfie to Samantha: The Next Trillion-Dollar Behavior