You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

WP_Term Object

(

[term_id] => 157

[name] => EDA

[slug] => eda

[term_group] => 0

[term_taxonomy_id] => 157

[taxonomy] => category

[description] => Electronic Design Automation

[parent] => 0

[count] => 4466

[filter] => raw

[cat_ID] => 157

[category_count] => 4466

[category_description] => Electronic Design Automation

[cat_name] => EDA

[category_nicename] => eda

[category_parent] => 0

[is_post] =>

)

There’s never a dull moment in the foundry race to offer FinFET processes that enable leading-edge SoC design. Today I attended a webinar hosted by Samsung and Synopsys on how to enable 14nm FinFET design. The two speakers were Dr. Kuang-Kuo Lin from Samsung and Dr. Henry Sheng from Synopsys.

Dr. Kuang-Kuo Lin, Samsung

Dr.… Read More

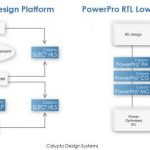

This year for DAC, Calypto has assembled an impressive lineup of customer presentation, suite sessions and Designer Tracks. To start with customer presentation, Steve Kommrusch, Fellow Design Engineer from AMD will be giving a talk in the Calypto Suite on AMD’s methodology for low power and will show how AMD was able to get further… Read More

Competition in EDA is absolutely necessary in order for the fabless semiconductor ecosystem to thrive. AMS tools with a low learning curve, high interoperability, and a powerful user interface improve design team productivity and enable a low total cost of ownership. That is why Tanner EDA has shipped over 33,000 licenses of … Read More

One of the best things about being part of SemiWiki is the exposure to new technologies and the people behind them. SemiWiki now works with more than 35 companies and I get to spend time with each and every one of them. Much like I do, IROC Technologies works closely with the foundries and the top semiconductor companies so it was a pleasure… Read More

Recently, Forte Design Systems announced the release of a new core engine to their popular high-level synthesis tool offering. It is a large undertaking, so I asked John Sanguinetti, Forte’s CTO, to answer some questions about that development effort.

Q. How long has it been since the last major upgrade of the Cynthesizer… Read More

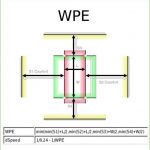

In advanced process technologies, electrical and timing problems due to variability can become a big issue. Due to various processing effects, a circuit performance (both speed and power) is dependent on specific layout attributes and can vary a lot from instance to instance. The accumulated effects can be severe to the point… Read More

With the support of the Heart of Technology, one of the big events this year at DAC will be the Kickin’ It Up in Austin celebration on June 3, at the amazing, world famous Austin City Limits Live! The event starts at 8:00 PM, runs until 1:00 AM and features three bands – 9-time Grammy winner Asleep at the Wheel; Vista Roads, an industry… Read More

This year’s version of Bill Deegan’s DAC App for iPhone is now available for download from the iTunes App Store. The App has the entire calendar included, and makes it easy to add any interesting looking event to your calendar. The whole exhibit hall can be searched and there is a zoomable map of the exhibit hall.

I have… Read More

Two weeks ago I blogged about analog verification and it started a discussion with 16 comments, so l’ve found that our readers have an interest in this topic. For decades now the Digital IC design community has used and benefited from regression testing as a way to measure both design quality and progress, ensuring that first… Read More

I talked with a mystery person earlier this week. I would love to tell you his (or her) name and the company he (or she) works for but they are the sort of company that doesn’t casually endorse any suppliers so it all has to remain anonymous. But they have been a customer of Pinpoint, originally from Tuscany Design Automation until… Read More

From the Selfie to Samantha: The Next Trillion-Dollar Behavior