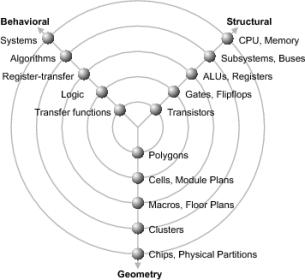

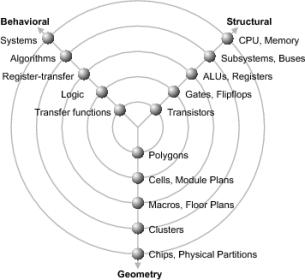

Thirty years ago in 1983 Professor Daniel Gajski and Kuhn created the now famous Y-Chart to show the various levels of abstraction in electronic system design:

We can still use this Y-Chart today because it still pertains to how engineers are doing their SoC designs. Along the Behavioral axis there is a need to know that each level of abstraction is really equivalent to the other levels to ensure that the design is consistent, and that no errors have crept into the design that may have been caused by:

- Addition of DFT structures

- Addition of low-power techniques, like clock gating

- Changes in cells during timing closure

- Engineering Change Orders

- Manual netlist changes

One brute force approach is to run functional simulation and re-use your test benches on each level of behavioral models. Well, that approach takes a lot of time, and still is not guaranteed to find all logical differences between two levels of models.

A more elegant approach is to run a class of EDA tools known as Equivalency Checking (EC), which take a mathematical approach to prove equivalency between two levels. Using Equivalency Checking has traditionally had a few limitations:

- Slow run-time speeds

- Limited capacity

- Complexity in terms of learning and setup

Where there’s a need there’s an opportunity, so the software engineers at Oasys have worked to address each of these three limitations by adding new features to EC like: hierarchy, automatic partitioning and parallel multi-processing. With these new technical features you can use EC with:

- Faster run-time speeds

- Higher capacity by scaling

- Simplicity in use

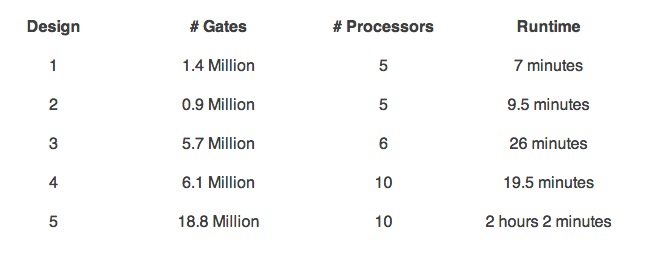

Let’s look at some actual numbers using this new EC approach:

The Oasys tool name is called RealTime Parallel EC, and their tool can simultaneously verify sub-blocks in a hierarchical design, so the run-times will scale linearly with the number of processors available.

lang: en_US

If you travel to DAC then plan on visiting Oasys in booth #1231 to get your questions answered.

Oasys is a privately held company that was founded in 2004 by a team of leading RTL synthesis developers from Ambit and Cadence. The team created a next generation physical RTL synthesis platform that empowers SoC/ASIC design teams to conquer the timing, power, area, and routability challenges of today’s complex SoCs, ASICs, and IP blocks. Oasys RealTime synthesis optimizes at a higher level of abstraction (the RTL level vs. gate level with other synthesis tools) enabling it to provide up to 10x faster turnaround times and the capacity to synthesize the entire top level of the largest SoC’s, ASICs or IP blocks, all while being physically aware for better correlation with physical design.

The company is funded by Intel Capital, Xilinx Ventures, and several private investors. The first product from Oasys, RealTime Designer, was launched in 2009 and is being used successfully by many of the top semiconductor vendors worldwide. The company’s newest product, RealTime Explorer, provides a unique capability for SoC/ASIC front end design teams to quickly identify and resolve top-level timing and routability issues before RTL hand-off to the back-end groups for synthesis and physical design implementation reducing schedules by an average of 1-2 months.

The Semiconductor Growth Numbers are Insane but the Real World Doesn’t Tally!