Designing at the 20nm node is harder than at 28nm, mostly because of the lithography and process variability challenges that in turn require changes to EDA tools and mask making. The attraction of 20nm design is realizing SoCs with 20 billion transistors. Saleem Haider from Synopsys spoke with me last week to review how Synopsys… Read More

Electronic Design Automation

Reduce Errors in Multi-threaded Designs

Many advanced algorithmic IPs are described in C++. We use this language because of its flexibility. Of course software algorithms are written to be executed on processors so they don’t solve all the issues of getting the algorithm implemented in hardware directly. This is not simply a high-level synthesis (HLS) issue. Usually… Read More

Properly Handing Of Clock Tree Synthesis Specifications

Given today’s design requirements with respect to low power, there is increasing focus on the contribution to total power made by a design’s clock trees. The design decisions made by the front-end team to achieve high performance without wasting power must be conveyed to back-end team. This hand-off must be accurate… Read More

Using Virtual Platforms to Make IP Decisions

Most SoC designs these days consist largely, but not entirely, of purchased IP blocks. But there are lots of tradeoffs involved in selecting IP blocks, and since those tradeoffs change with process node, even decisions that seem “obvious” based on the last generation of the design, may not be so clear cut. Even if you… Read More

TSMC ♥ Solido

Process variation has been a top trending term since SemiWiki began as a result of the articles, wikis, and white papers posted on the Solido landing page. Last year Solido and TSMC did a webinar together, an article in EETimes, and Solido released a book on the subject. Process variation is a challenge today at 28nm and it gets worse… Read More

Mentor CEO Wally Rhines U2U Keynote

You will never meet a more approachable CEO in the semiconductor ecosystem than Dr. Walden C. Rhines. The first time I met Wally was way back when I blogged for food and he invited me over for lunch. Even better, a year or two later I was having dinner with a friend at the DBL Tree in San Jose. Wally was waiting for his flight home so he joined… Read More

When installing a sink, it’s a lot faster to buy a saw

Mentor’s announcement from Design West this week pretty much signals the end of standalone ESL tools, in favor of more useful stuff. They have pulled the pieces of their Sourcery CodeBench environment along with their embedded Linux offering and their Vista virtual prototyping platform into a native embedded software development… Read More

Best Practice for RTL Power Design for Mobile

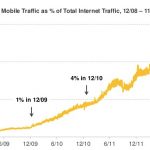

Mobile devices are taking over the world. If you want lots of graphs and data then look at Mary Meeker’s presentation that I blogged about earlier this week. The graph on the right is just one datapoint, showing that mobile access to the internet is probably up to about 15% now from a standing start 5 years ago.

Of course, one obvious… Read More

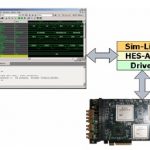

10 to 100X faster HDL Simulation Speeds

Speed, capacity, accuracy – these are the three major EDA tool metrics that we pay attention to and that enable us to design and verify an SoC. Talk to any design or verification engineer and ask if they are satisfied with the time that it takes to simulate their latest design, or to verify that it meets spec and is functionally… Read More

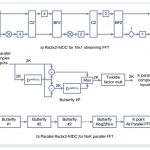

Gigahertz FFT rates on a 500MHz budget

A basic building block of any communication system today is the fast Fourier transform, or FFT. A big advantage of FPGA implementations of FFTs is they can be scaled and tuned for the task at hand, optimizing data flow, resource use, and power consumption. Scaled, that is, up to the clock speed of the FPGA – or so it would seem.

Today’s… Read More

Quantum Computing Technologies and Challenges