Recently, I discussed the increasing risk of metastability hazards at nanoscale geometries. These risks are significantly aggravated at low supply voltages and low temperatures and must be addressed during the design cycle of any mission critical application. This time I discuss what it takes to estimate a synchronizer’s … Read More

Electronic Design Automation

Derivative Designs Need Tools Too

Increasingly, SoC designs consist of assembling blocks of pre-designed IP. One special case is the derivative design where not just the IP blocks get re-used but a lot of the assembly itself. For example, in the design below some blocks are added, some blocks are updated, some hierarchy is changed. But the bulk of the design remains… Read More

Increasing Automotive Semiconductor Test Quality

The growing amount of electronics within today’s automobiles is driving very high quality and reliability requirements to a widening range of semiconductor devices. At the same time, traditional fault models are becoming less effective at achieving desired silicon quality levels. Improvements in test solutions are needed… Read More

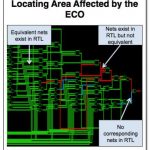

Formality Ultra, Streamline Your ECOs

One of the most challenging stages in an SoC design is achieving timing closure. Actually design closure is perhaps a better term since everything needs to come together such as clock tree, power nets, power budget and so on. Changes made to the design are known as ECOs (which stands for engineering change orders, a term that comes… Read More

Swap and Play Extended To Chip Fabric and Memory Controllers

Virtual platforms enable software development to take place on a model of an electronic system. What everyone would like is models that are fast and accurate but that is simply not possible. Fast models are fast because they don’t model everything at the signal level. And accurate models get to be accurate by handling a lot of detail… Read More

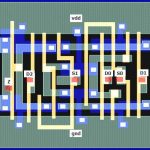

Eldo and Pyxis from Mentor, DAC Update

Last Monday at DAC I met with Linda Fosler, Marketing Director at Mentor Graphics to get an update on what’s new with Eldo(Circuit simulator) and Pyxis (custom IC layout and schematic).

Linda Fosler, Mentor Graphics… Read More

Calibre Update at DAC

Mentor Graphics throws a very nice dinner party at DAC each year for journalists, bloggers and top customers, so this year I spoke with Michael Buehler-Garcia about what’s new with Calibre.

Michael Buehler-Garcia, Mentor Graphics

… Read More

GPU-Based SPICE Simulator for Library Characterization

Jeff Tuanis the CEO and President of an EDA startup called G-Analog, founded in May 2012. His background includes working at: Cadence, Epic, Synopsys, Nassda, Chartered Semi and GLOBALFOUNDRIES. Jason Lu is the R&D manager. We met at DAC last week to talk about his company’s new product called Gchar for IC library characterization… Read More

Missed #50DAC? See Aldec Verification Sessions Online

Aldec, Inc. is an industry-leading Electronic Design Automation (EDA) company delivering innovative design creation, simulation and verification solutions to assist in the development of complex FPGA, ASIC, SoC and embedded system designs. With an active user community of over 35,000, 50+ global partners, offices worldwide… Read More

Increase Your Chip Reliability with iROC Tech

As we have moved towards extremely low process nodes with very high chip density, the cost of mask preparation also has become exorbitantly high. It has become essential to know about the failure rates and mitigate the same at the design time before chip fabrication, and also to make sure about chip reliability over time as it is constantly… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center