You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

WP_Term Object

(

[term_id] => 157

[name] => EDA

[slug] => eda

[term_group] => 0

[term_taxonomy_id] => 157

[taxonomy] => category

[description] => Electronic Design Automation

[parent] => 0

[count] => 4439

[filter] => raw

[cat_ID] => 157

[category_count] => 4439

[category_description] => Electronic Design Automation

[cat_name] => EDA

[category_nicename] => eda

[category_parent] => 0

[is_post] =>

)

In a recent article I discussed how easy it was to debug SystemC source code as shown in a video published on YouTube by Forte Design Systems. I also commented on the usefulness of the well-produced Forte video series. Today, I am reviewing another video in that series on analyzing high-level synthesis (HLS) results.

Cynthesizer… Read More

A Goldmine of Tester Databy Beth Martin on 07-10-2013 at 2:06 pmCategories: EDA

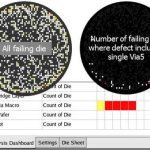

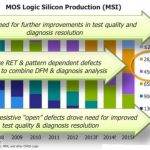

Yesterday at SEMICON West I attended an interesting talk about how to use the masses of die test data to improve silicon yield. The speaker was Dr. Martin Keim, from Mentor Graphics.

First of all, he pointed out that with advanced process nodes (45nm, 32nm, and 28nm), and new technologies like FinFETs, we get design-sensitive defects.… Read More

EDA companies produce a wealth of content to help IC engineers get the best out of their tools through several means:

- Reference Manuals

- User Guides

- Tutorials

- Workshops

- Seminars

- Training Classes

- Phone Support

- AE visits

…

Read More

At Semicon yesterday I attended Mentor’s presentation on improving test standards. Joe Sawicki was meant to present but he was unable to get a flight due to the ongoing disruption at SFO after last weekend’s crash. I just flew in myself and it is odd to see the carcase of that 777 just beside the runway we landed on.

The … Read More

Calypto 2013 Reportby Paul McLellan on 07-05-2013 at 5:48 amCategories: EDA

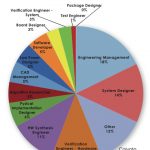

Each year Calypto runs a survey of end-users. This year’s survey and report has two parts, power reduction and high level synthesis (HLS).

The topics covered are:

- survey methodology and demographics

- top methods used to reduce power

- engineering time spent on specfiic RTL tasks to reduce power

- plans to deploy RTL power reduction

…

Read More

Easy SystemC Debuggingby Randy Smith on 07-03-2013 at 7:00 pmCategories: EDA

Electronic system design has been slowly migrating to higher level languages such as SystemC for more than a decade now. SystemC is an open source C++ library that has emerged as a standard for high-level design and system modeling. Writing code in SystemC has several advantages which I won’t elaborate on in this article, though… Read More

If DAC is the most general event in our industry, then the LicenseMonitor Users’ Group Silicon Valley has to be one of the most focused. It was held back in May but one of the key presentations was Brian Janes of RTDA talking about what is new in the latest version of LicenseMonitor which is 2013.03.

Like a number of people at RTDA,… Read More

IR drop analysis across your board, package and SoC ensures that your Power Delivery Network (PDN) is robust, and that your system will function to spec. There are both static and dynamic approaches to IR drop analysis of a full-chip with billions of transistors, while the dynamic approach produces the most accurate results compared… Read More

Grenoble is French city well-known within the Semiconductor industry to be one of the last location counting wafer fabs, not only in France but in fact in Europe. Back in the 70’s, under French government impulse, through the Commisariat à l’Energie Atomique (CEA) and the LETI subsidiary in charge of Electronic related research,… Read More

Is it possible to design a processor with very high performance and low power consumption? To answer that, embedded illuminati are now focusing on designs tuned to specific workloads – creating a tailored processor that does a few things very efficiently, with nothing extra.… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center