In the modern electronic world, it’s difficult to imagine any system working as a whole without MEMS (Micro-electromechanical Systems) such as pressure sensors, accelerometers, gyroscopes, microphones etc. working in sync with other ICs. Specifically in AMS (Analog Mixed-Signal) semiconductor designs, there can be significant… Read More

Electronic Design Automation

TSMC ♥ Mentor (Calibre PERC)

As semiconductors become more integrated into our lives reliability is becoming a critical issue. As IP consumes more of our die, IP reliability is becoming a critical issue. As we pack more transistors into a chip, reliability is becoming a critical issue. As we move from 28nm to 20nm to 16nm, reliability is becoming a critical … Read More

Diagnosing Double Patterning Violations

I’ll bet you’ve read a bunch of stuff about double patterning, and you’re probably hoping that the design tools will make all your double patterning issues just go away. Well, the truth is that the foundries and EDA vendors have worked really hard to make that true.

However, for some critical portions of your design, there … Read More

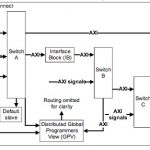

Getting the Most Out of the ARM CoreLink™ NIC-400

SoC designers are attracted to ARM as an IP provider because of their popular offerings and growing ecosystem of EDA partners like Carbon Design Systems. At the upcoming ARM Techcon on October 31 this week in Santa Clara you’ll have an opportunity to hear a joint presentation from ARM and Carbon Design Systems on: Getting … Read More

Cadence’s Mixed-Signal Technology Summit

On October 10, I attended another Cadence Summit, this one titled the Cadence Mixed-Signal Technology Summit. Recently, I had written about the Cadence Silicon Verification Summit. The verification event was the first of its kind, and I thought it had terrific content. Being more of a digital guy myself, I was unaware that Cadence… Read More

An easier way to deal with design rule waivers (video)

At advanced nodes, design rules are necessarily more complex and restrictive. Although most of the time you can find a way to live with them, sometimes it’s necessary to seek a waiver from the foundry for a particular design feature. This involves documenting the feature, the design rules in question and the conditions under which… Read More

An Affair to Remember: EDA’s 50th Anniversary

What an amazing night! I celebrated the 50[SUP]th[/SUP] anniversary of the industry I grew up in! With my beautiful wife at my side and a table full of friends we all went down memory lane, ate, drank, and then enjoyed the auction.

The tour of the new computer museum was amazing. I was learning so much up until the 1970’s, then … Read More

TSMC ♥ Synopsys (HSPICE)

In case you haven’t noticed, Synopsys has been in the press lately talking about their relationship with TSMC. Since I’m an internationally recognized industry expert they gave me a call for a briefing and I was happy to do it. Staying connected with the #1 EDA company is important and fun since I get to ask questions that most people… Read More

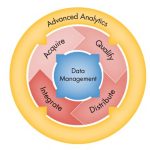

Webinar on IP Lifecycle Management

EDA and Semiconductor companies are offering new webinars almost every week of the year, so there’s always something worth learning about that only takes an hour of time. On November 5th there’s an interesting webinar planned on the topic of IP Lifecycle Management, hosted by Methodics. I blogged two weeks ago about,… Read More

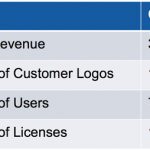

Kathryn: "Formal Will Dominate Verification"

At the Jasper Users’ Group meeting, Kathryn presented the state of Jasper. The numbers are impressive. The company has grown at a CAGR of over 35% since 2007, which is 6 times faster than EDA as a whole. They have been profitable at 15-20% EBITDA for 14 consecutive quarters.

Jasper is focused on engaging deeply with a small number… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center