In the 1990’s there was a push to build EDA frameworks, however they all failed because no user wanted to be locked into one EDA vendor tool flow. Fast forward to 2014 and there’s an emerging trend to use web-based EDA tools as a framework, instead of downloading and installing software to your desktop or device. I just… Read More

Electronic Design Automation

A New Digital Place and Route System

IC place and route tools can be very high-priced EDA software to purchase or lease, so there’s some good news for AMS designers that need an affordable digital place and route tool for their mostly analog designs. Today the team at Tanner EDAannounced a totally new place and route system has been added to their Schematic Driven… Read More

SEMulator3D 2014 – New Enhancements for Virtual Fabrication in the 3D IC Era

A Virtual Platform for any kind of design or manufacturing in any discipline of science or engineering (electrical, mechanical, aeronautics etc.) must be able to provide an accurate representation of an actual design/product in a fraction of time and cost it takes to build working prototypes. In the case of semiconductors at … Read More

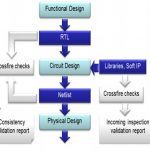

Semiconductor IP Validation Gets Faster

Semiconductor IP continues to grow in use for SoC design, and many chips can now use hundreds of IP blocks from multiple vendors. Validating the quality of the IP blocks is an important step in the design process, and you could perform manual validation and inspection of each new IP block at the expense of time and engineering effort.… Read More

EDAC Mixer: Sonoma Chicken Coop

Get together with your fellow industry peers and insiders at the monthly EDAC Mixer, to the benefit of local charities. You don’t need to donate anything, you just show up and pay for your own drinks. A portion of the proceeds will go to local charities, this month to the Resource Area for Teaching (RAFT), a San Jose based non-profit… Read More

Sketch Router and auto-assist PCB layout

Archaic tech metaphors abound, stuck in the psyche of users everywhere. We still “dial” numbers, long after the benefit of a short pull area code disappeared. (Humans could dial 1, 2, or 3 a lot faster on a rotary phone, and there were fewer dialpulses for central office switches to decode – thus big cities with more phone traffic like… Read More

Sebastian Thrun: Self-driving cars, MOOCs, Google Glass and more

Sebastian Thrun gave a fascinating keynote at SNUG last week. It didn’t have that much to do with IC design but he discussed 3 projects that he had been involved with. Anyone would be happy to have just one of these projects on their resume but he has all these (and more).

The first is the Google self-driving car. This project actually… Read More

Automating Analog Verification in Virtuoso

Digital designers have been automating the functional verification process for many years now, however when you talk to an analog designer about how they do verification you quickly realize that the typical process is quite ad-hoc and little automated. Necessity does create an opportunity so the software engineers at Methodics… Read More

Jasper Announces Sequential Equivalence Checking

Jasper finally announced their sequential equivalence checking app this morning. I say finally because they haven’t really tried to keep it a secret. They talked about it at the end of last year the Jasper User Group meeting and it has even had a page on their website. But formally the product was announced today.

The new JasperGold… Read More

Bye-Bye DDRn Protocol?

In fact, this assertion is provocative, as the DDR4 protocol standard has just been released by JEDEC… after 10 years discussion around the protocol features. Yes, the first discussions about DDR4 have started ten years ago! Will DDR4 be used in the industry? The answer is certainly yes, and DDR4 will most probably be used for years.… Read More

Quantum Computing Technologies and Challenges