You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

WP_Term Object

(

[term_id] => 157

[name] => EDA

[slug] => eda

[term_group] => 0

[term_taxonomy_id] => 157

[taxonomy] => category

[description] => Electronic Design Automation

[parent] => 0

[count] => 4442

[filter] => raw

[cat_ID] => 157

[category_count] => 4442

[category_description] => Electronic Design Automation

[cat_name] => EDA

[category_nicename] => eda

[category_parent] => 0

[is_post] =>

)

Next week Mike Jensen of Mentor will present a webinar Improving Complex System Design Reliability and Robustness. The webinar will be presented live twice and presumably available for replay soon after, as is usually the case:

- September 4th 6.00-6.45am pacific (9pm in Asia, 3pm in most of Europe)

- September 4th 10.00-10.45am

…

Read More

Metal fill requirements for inductors are now a fact of life. Fill has long been seen as detrimental to device performance due to parasitic capacitance. The necessity of fill arises from the need to ensure planarization of dielectric layers by using chemical mechanical polishing. Without adequate fill, areas of the chip can suffer… Read More

Most analog designers are aware of loops stability. In most cases, stability is understood as AC stability, the goal is ensuring enough phase (gain) margin so as to avoid the loop to enter oscillation. But prior to studying AC stability, DC stability should be questioned. What is that DC stability only few people think of?… Read More

Mentor’s results came out last week. They were good. Wally opened the call:Thanks. Once again results for Mentor Graphics in the quarter exceeded our guidance. Revenue of $260.2 million and non-GAAP earnings per share of $0.23, were ahead of our guidance of $250 million and $0.15 earnings per share. Strength in bookings… Read More

Raising four children is no easy task, believe me. My beautiful wife and I always felt it was important to foster the charitable side of our children by volunteering at the food bank, cleaning up local waterways, and other activities we could do as a family. To be clear, that is why my family did the ALS Ice Bucket Challenge.

“It is amazing… Read More

In this age of electronics, especially with so many different types of human held devices and more upcoming wearable devices, it’s utmost important to protect the massive circuitry inside those tiny parts in the devices from ESD related failures. The protection needs to happen at all stages – cells inside the chips, package… Read More

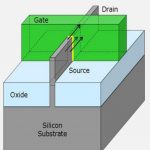

Planar CMOS processes have been offered for decades now, and all the way down through the 28nm node it has been riding the benefits of Moore’s Law. A few years back we started hearing from Intel about TriGate (aka FinFET) starting at the 22nm node as a way to use a more 3D processing approach for transistors instead of planar CMOS.… Read More

Motion sensors are also commonly applied in a broad range of consumer products, including smartphones, wearable devices, game controllers and sports watches, with applications ranging from screen orientation to indoor navigation. If you desire to build an Inertial Measurement Unit (IMU) to efficiently compute 3D orientation,… Read More

Design engineers frequently struggle with transmission line design and modeling. We can define a length of interconnect that contains more than 1/100th of a wavelength as a transmission line. This seems to be the breakpoint where distributed effects to start to become significant. To improve circuit performance these long … Read More

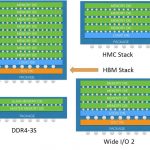

The DRAM market is shaking… In 2014, analysts predict that LPDDR4 will surpass DDR4 for the first time. When releasing DDR4 standard, JEDEC has clearly stated that the industry should not expect any DDR5. Does this means that DRAM technology new development is ending with DDR4? According with Mike Howard, principal analyst at … Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center