Very recently, I was seeing intense discussions on the need for agile hardware development just like agile software and ideas were being sought from experts as well as individuals. While in software world it has already evolved, in hardware world it’s yet to see the shift in paradigm. My point is that the end goal of agile hardware… Read More

Electronic Design Automation

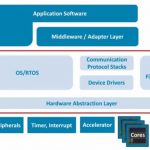

3 reasons to focus on hardware dependent software

Why is software for modern SoCs so blasted expensive to develop? One reason is more software is being developed at the kernel layer – hardware dependent software, or HdS. Application software often assumes the underlying hardware, operating system, communication stacks, and device drivers are stable. For HdS, this flawed assumption… Read More

A Brief History of ASTC and VLAB Works

When I worked for VaST our engineering was in Sydney Australia. To my surprise there was another, entirely independent, group working on virtual platform modeling and tools in another place in Australia, in Adelaide. Is there something in the Fosters? They had originally been part of Motorola Corporate R&D and Software Group,… Read More

ANSYS Electronics Simulation Expo – A View from Industry

As we are seeing more and more automation in most of our activities, not only through software but also smart electronics (at cutting-edge technologies) equipped with processors, micro-controllers, sensors and so on which make a whole system as an integrated entity on a small piece of semiconductor intertwined with other systems… Read More

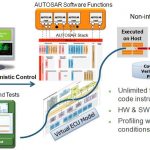

Virtual Platform Powers AUTOSAR Software Development

As a significant part of our life is spent in travelling, it’s natural that automotive sector continues to get traction with a significant push towards electronics and automated solutions for automobiles such as cars to provide safety, comfort and entertainment. These solutions are provided by complete systems which operate… Read More

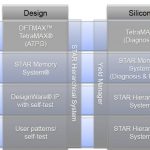

Two New Announcements at ITC from Synopsys

Each year at the International Test Conference(ITC) we hear about the latest advances from the testability side of both EDA vendors and academics. This year Aart de Geus, Chairman and Co-CEO of Synopsys delivered a keynote speech titled, “Testing Positive, for Complexity“. Yesterday I spoke with Robert Ruiz and… Read More

Crossfire on Continuous Path of Improvement

In an ever growing world of IPs, it’s essential that a tool which vouches to simplify designer’s job of IP development and help improving its quality remains versatile to encompass various formats, databases, common data models, standard libraries, scripting etc. that are used in the development of IPs and their exchange between… Read More

How Lucio Lanza Got Into EDA

Lucio Lanza is this year’s recipient of the Kaufman award. Unlike most recipients, Lucio worked closely with Phil Kaufman earlier in his career. I met with him at his office in Palo Alto to hear the story.

Even if you have never met him, it would be a reasonable guess from his name that Lucio Lanza is Italian. And you’d be right. He grew… Read More

Power Management Policies for Android Devices

I’ll never forget the shock when I upgraded from a Feature Phone to my first Android-powered SmartPhone, because all of a sudden my battery life went from 6 days down to only 1 day between charges. As a consumer, I really want my battery to last much longer than one day, so the race is on for mobile phone companies to design their… Read More

A Complete Scalable Solution for IP Signoff

In an SoC world driven by IP, where an SoC can have hundreds of IP (sourced not only from 3[SUP]rd[/SUP] party but also from internal business units which can have a lot of legacy) integrated together, it has become essential to have a comprehensive and standard method to verify and signoff the IP. Additionally, these checks must … Read More

Captain America: Can Elon Musk Save America’s Chip Manufacturing Industry?