When I drive down to Silicon Valley I usually listen to podcasts rather than just listen to the radio. One that I especially like is Russ Robert’s EconTalk, which has an hour-long episode every Monday morning on a wide range of different aspects of Economics. Normally he interviews an economist. He has also interviewed the… Read More

Electronic Design Automation

The Magnificent Seven of International IP Management

Almost all large projects these days are distributed across multiple geographic locations. As the world rotates underneath the sun, the focus of activity moves too: Europe, US, China, India, back to Europe. For this to work effectively requires a collaborative platform designed for multi-site design efforts, a platform that… Read More

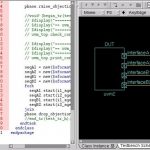

Never Imagined So Easy Class-based Testbench Debugging

When it comes to debugging a design testbench organized in object-oriented style with objects, component hierarchies, macros, transactions and so on, it becomes an onerous, tasteless, and thankless task for RTL verification engineers who generally lag in software expertise. Moreover, class-based debugging tools have lagged… Read More

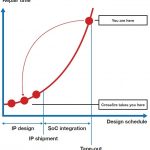

ClioSoft SOS v7.0: Faster, Smarter and Stronger

System-on-chips (SoCs) are now everywhere, whether they are processors, microcontrollers or FPGAs, and what matters more these days is how quickly these large and complex chips adapt to the specific needs of the OEM application or the “system.” So time-to-market window is shrinking, and conversely, the use of … Read More

Foolproof Your IP before it Stumbles in Higher-up Design

SoC designs are increasingly becoming assemblies of a large number of IP blocks. A well integrated assembly can lead to a successful PPA (Power, Performance and Area) optimized design. However, it is equally important that each IP block is optimized, robust, and integrable in the design. The complexity of an IP and its integration… Read More

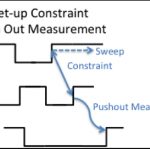

Ultra-low Voltage: Is Your Slack Really Positive? Are You Sure?

During synthesis and static timing the main figure of merit is “slack”. If a signal arrives with time to spare before it is needed (often measured against the setup time before a clock changes at a register) then the slack is positive. Positive slack is generally a good thing, although it can indicate over-design if … Read More

An Open Letter to Qualcomm CEO

Dear Steve,

Let me first clarify about myself that I am a humble blogger at Semiwiki and admire your company as the #1 Semiconductor Fabless Company and #4 in terms of overall semiconductor sales of the top10 semiconductor companies in the world as per 2014 data. Also, I must mention another point of admiration that your company is… Read More

Acoustic Resonators for RF: MEMS with No Moving Parts

There is an annual conference known officially as the Sensors and Actuators Workshopand informally as Hilton Head since it is held on Hilton Head island in South Carolina. Coventor talked to some of the top researchers last year about RF filters and decided to develop a simulation solution that would better serve both the researchers… Read More

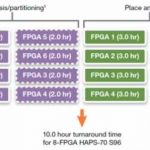

More FPGA-based prototype myths quashed

Speaking of having the right tools, FPGA-based prototyping has become as much if not more about the synthesis software than it is about the FPGA hardware. This is a follow-up to my post earlier this month on FPGA-based prototyping, but with a different perspective from another vendor. Instead of thinking about what else can be done… Read More

John Koeter: How To Be #1 in Interface IP

John Koeter is in charge of marketing Synopsys’ IP and prototyping solutions. I talked to him last week.

He grew up in upstate New York, son of a Scottish mother and a Dutch father who immigrated to the US, so he is first generation American, unlike everyone else I’ve interviewed so far for this series who were born overseas.… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center