The Internet of Things (IoT) is creating urgent demand for a new generation of analog/mixed-signal (AMS) designs, some of which also contain MEMs. To efficiently create the myriad of AMS devices at the edge of the IoT requires a design environment that is affordable and easy to use, but powerful enough to create the widely diverse… Read More

Electronic Design Automation

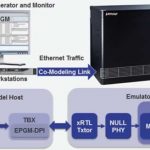

Testing Ethernet with virtual co-modeling

Ethernet is suddenly a hot topic in SoC design again. The biggest news may be this: it’s not just the cloud and enterprise networks. Those are still important applications. The cloud is driving hard for more ports at 25G server and 100G switch speeds according to a recent Dell’Oro Group report. Enterprise networks are driving for… Read More

My Experience with the Ultra Thin 2015 MacBook

Before we left for our 5 week trip to Europe I decided that I would need a real laptop computer on the road. I knew it would be a near necessity for booking hotels and making train reservations. Also, I would need to write emails and maybe even pay some online bills. I already have an iPad but really wanted to be able to run all my applications… Read More

A Complete Simulation Platform for Mobile Systems

If we take an insight into the semiconductor industry, we can easily find that mobile systems are the main drivers of this industry. The Smartphone business has remained at the top since a good number of years. Although the Smartphone sales growth has started showing a sign of stagnation, it is still a main contributor with a solid… Read More

A Paradigm Shift in Microelectronic System Design

A Paradigm Shift

The word “paradigm” is defined in the dictionary as “a framework containing the basic assumptions, ways of thinking, and methodology that are commonly accepted by members of a scientific community”. In his influential book “The Structure of Scientific Revolutions” published in 1962, Thomas Kuhn uses the term… Read More

Four Things a New Semiconductor Technology Must Have to be Disruptive

This post discusses attributes of gallium nitride (#GaN) that make it a disruptive technology and identifies the four factors required for GaN technology to displace silicon as the technology of choice.

Displacing the Silicon with GaN

38 years ago, when I first entered the semiconductor business as a freshly minted Stanford … Read More

Mentor 2Q Results

So it was Mentor’s turn yesterday after Synopsys on Wednesday. And yes, it really is the end of their second quarter. They produced some very good results. As Wally opened:The second quarter of fiscal 2016 was one of record for Q2. We substantially exceed our own expectations was revenue of $281.1 million and non-GAAP earnings… Read More

Older Nodes Get New Life With Ultra Low Power Variants for IoT

Ever since I can remember, and I’ve been in EDA since the early 80’s, new process development has largely focused on the latest nodes. Trailing nodes were quickly put into support mode. New nodes benefited the most from static and dynamic voltage reduction efforts, as well as improvements in flows and performance. Only a small number… Read More

Synopsys Q3 Results

Synopsys announced their quarterly results this afternoon. It is the end of their Q3 (yes, they are not on the regular calendar year. Neither, for that matter, is Mentor who announce tomorrow). On the earnings call Aart started off:Good afternoon. I’m happy to report that our third quarter results were very strong, as we achieved… Read More

My Tryst with Semiconductors and EDA

Yes, today I realize it feels like a tryst with semiconductors. In actual meaning; it wasn’t a love affair with semiconductors, but I must say the greatest thing it taught me about how it approaches towards perfection. And that became the guiding principle in my life; how can I do something better. Of course nothing is perfect in life… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center