The Server SoC at the heart of Data Center almost don’t care about power consumption, at the opposite of Application Processors for smartphone. If you design a server multi-core SoC, you target the highest performance, in fact a combination of high frequency and lowest possible latency, and try to pack as many CPU core and embedded… Read More

Electronic Design Automation

Supernovae and Safety

Whenever we push the bounds of reliability in any domain, we run into new potential sources of error. Perhaps not completely new, but rather concerns new to that domain. That’s the case for Single Event Upsets (SEUs) which are radiation-triggered bit-flips, and Single Event Transients (SETs) which are radiation-triggered pulses… Read More

Pathfinding to an Optimal Chip/Package/Board Implementation

A new term has entered the vernacular of electronic design engineering — pathfinding. The complexity of the functionality to be integrated and the myriad of chip, package, and board technologies available make the implementation decision a daunting task. Pathfinding refers to the method by which the design space of technology… Read More

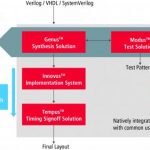

Cadence Adds New Dimension to SoC Test Solution

It requires lateral thinking in bringing new innovation into conventional solutions to age-old hard problems. While the core logic design has evolved adding multiple functionalities onto a chip, now called SoC, the structural composition of DFT (Design for Testability) has remained more or less same based on XOR-based compression… Read More

Updated tool cuts through DO-254 V&V chaos

Audits. The mere mention of the word keeps project managers up at night and sends most designers running. However, in the case of FPGA designs seeking DO-254 compliance, the product doesn’t ship until the audit is complete – there is no avoiding it, or skating around it.… Read More

Expanding 3D EM Simulation Access to All

James Clerk Maxwell’s eponymous equations are the basis for simulating electromagnetic wave propagation. In school, EE majors tended to fall into two camps: (a) those that thoroughly enjoyed their fields and waves classes, who liked doing surface integrals, and who were adept at demonstrating the “right hand rule”, and (b) … Read More

HSPICE – 35 and looking good!

A maturetool. A legacytool. A tool that’s a little long in the tooth. We have all used these terms to refer to an EDA product that has not been able to keep up with technical challenges of model complexity, performance, or new features required by current SoC and system design requirements.… Read More

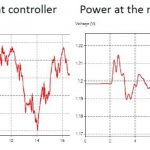

DesignCon 2016 — signal integrity must be power-aware!

DesignCon is a unique conference — its tagline is “Where the Chip meets the Board”. Held each January in Santa Clara, the conference showcases a wealth of new technologies for advanced packaging, printed circuit board fabrication, connectors, cables, and related analysis equipment (e.g, BERT, VNA, scopes). Of specific… Read More

The Mechanical Reliability of IC Packages

At Intel back in the late 1970’s we were designing DRAM chips and mounting them in ceramic and plastic packages, however there were problems when some of the die would crack inside of the package because of thermal mismatch issues with how the die was attached to the heat spreader inside the package. Back then we really didn’t… Read More

5nm Chips? Yes, but When?

For any invention, technical proof of concept or prototyping happens years ahead of the invention being infused into actual products. When we talk about 5nm chip manufacturing, a test chip was already prototyped in last October, thanks to Cadence and Imec. Details about this chip can be found in a blog at Semiwiki (link is given … Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center