Platform Design Automation, Inc (PDA). recently closed a US$6 million pre Series A investment round, and the company has shifted its focus from providing SPICE modeling related software and services to forming a complete AI-driven ecosystem from probing to simulation. Albert Li was the GM of Accelicon, a leading EDA tool and … Read More

Electronic Design Automation

Cadence Design Secures Photonic Beachhead

I had the privilege to attend a five-day PIC (photonic integrated circuit) training hosted by 7-Penniesand Tektronix in San Jose, CA this week. This training was quite comprehensive and covered photonic materials and platforms, design automation, fabrication, packaging and test. It also included invited talks from photonic… Read More

ATPG, Automotive and 7nm FinFET

The state of Texas hosted two or our industry’s big technical conferences and trade shows this year: DAC and ITC (International Test Conference). IC designers know about DAC in Austin, and test engineers know about ITC in Dallas. I travelled to Austin to cover DAC this past summer, and I was able to connect with Robert Ruiz … Read More

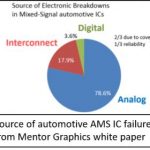

Mentor DefectSim Seen as Breakthrough for AMS Test

For decades, digital test has been fully automated including methodologies and automation for test pattern generation, grading and test time compression. Automation for analog and mixed-signal (AMS) IC test has not however kept pace. This is troubling as according to IBSapproximately 85% of SoC design starts are now AMS designs.… Read More

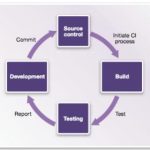

Embedded Agility

A familiar refrain in software development, as much as in hardware development, is that the size and complexity of projects continues to grow as schedules shrink and expectations of quality can increase dramatically. A common approach to managing this challenge in software programs is agile development practices and one aspect… Read More

Solido DA is One of Deloitte’s Fastest 50!

As a longtime EDA professional this really made my day. At a time where emerging EDA companies struggle for public validation, it warms my heart to see some very public recognition for an EDA job well done.

Deloitte, a leading Canadian professional financial services firm, announced the winners of their Technology Fast 50 program… Read More

Ford Motors Discusses Future Mobility Trends at Synopsys Seminar

Five or ten years ago it would have been hard to imagine someone from Ford Motors giving the keynote at a technology summit at a major EDA company like Synopsys. However, on November 2[SUP]nd[/SUP], Synopsys hosted a seminar on the topic of Automotive Architecture Design and System Testing, and Ford Technical Fellow Jim Buczkowski… Read More

IC Design Management: Build or Buy?

When I first started doing circuit design with Intel at the transistor level back in the late 1970’s we had exactly two EDA tools at our disposal: an internally developed SPICE circuit simulator, and a commercial IC layout system. Over the years at Intel the internal CAD group added many more automation tools: gate level simulator,… Read More

FPGAs allow customization of SEU mitigation

Teams working on avionics, space-based electronics, weapons delivery systems, nuclear generating plants, medical imaging equipment, and other applications where radiation leads to single-event upsets (SEU) are already sensitive to functional safety requirements. What about automotive applications?

With electronic… Read More

Improving on EMACS for VHDL Creation

OK – I admit I titled this piece as clickbait. There is a core of designers for whom belief in the supremacy of EMACS for RTL creation comes close to religion. Some will read only the title and jump immediately to penning searing comments questioning my intelligence, experience, parenthood and ability to tie my own shoes. Some, I hope,… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center