Automotive ICs have to operate in a very demanding environment in terms of both temperature and voltage ranges, along with the ability to withstand g-forces and be sealed from the elements. Not an easy design challenge. For many consumer ICs we see output drive currents on the IO pins measured in mA, however in automotive if you want… Read More

Electronic Design Automation

High Frequency Trading and EDA

Pop quiz – name an event at which an EDA vendor would be unlikely to exhibit. How about The Trading Show in Chicago, later this month? That’s trading as in markets, high-frequency trading, blockchain and all that other trading-centric financial technology. This is another market, like cloud, where performance is everything and… Read More

Building Better Digital Content Protection

Back in college my roommates figured out that the TV cable coax wire was still connected to our apartment. As a result, I was able to watch the Richard Pryor movie Silver Streak about 30 times without a cable box, however the screen was partially jumbled from the simple content protection used back then. This was possible by aggressively… Read More

Webinar: Next Generation Design Data & Release Management

Design Data Management (DDM) is a bit like insurance. It’s something every semiconductor company has to have, and as a result it’s probably something taken for granted. In order to make their products more useful, the DDM vendors have added more functionality to manage more of the lifecycle of design data.

Dassault’s Synchronicity… Read More

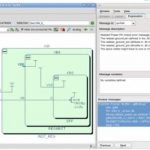

Power Checks for Your Libraries

When your design doesn’t work, who owns that problem? I don’t believe the answer to this question has changed significantly since semiconductor design started, despite distributed sourcing for IP and manufacturing. Some things like yield can (sometimes) be pushed back to the foundry, but mostly the design company owns the problem.… Read More

Webinar on TFT and FPD Design

I knew that the acronym for TFT meant Thin Film Transistors, but I hadn’t heard that FPD stands for Flat Panel Detectors. It turns out the FPD are solid-state sensors used in x-ray applications, similar in operation to image sensors for digital photography and video. I’ll be attending and blogging about what I learn… Read More

Polishing Parallelism

The great thing about competition in free markets is that vendors are always pushing their products to find an edge. You the consumer don’t have to do much to take advantage of these advances (other than possibly paying for new options). You just sit back and watch the tool you use get faster and deliver better QoR. You may think that… Read More

Circuit Design: Anticipate, Analyze, Exploit Variations – Statistical Methods and Optimization

We are happy to publish book reviews, like this one from Dr. Georges Gielen of the KU Leuven in Belgium, for the greater good of the semiconductor ecosystem. So, if you have a semiconductor book you would like to review for fame not fortune let me know.… Read More

Achieving Requirements Traceability from Concept through Design and Test

Excel is a wonderful, general purpose spreadsheet tool that lets me organize and analyze rows and columns of data into something meaningful, however it doesn’t know anything about requirements traceability for complex semiconductor projects. So why do so many engineering teams still rely upon Excel or custom, in-house… Read More

System-Level Power Estimation

When I first saw that Rob Knoth (Product Director at Cadence) had proposed this topic as a subject for a blog, my reaction was “well, how accurate can that be?” I’ve been around the power business for a while, so I should know better. It’s interesting that I jumped straight to that one metric for QoR; I suspect many others will do the same.… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center