Sometimes the hardest thing about bringing a new idea to fruition is overcoming the inertia to get started with a proof-of-concept. You must be able to put together enough parts of the solution to prove to those controlling budgets that an idea has merit and is worth taking to the next level. It’s a bit of a chick-vs-egg scenario as … Read More

Electronic Design Automation

A Brief History of PSS at Breker

Verification engineers are hearing a lot about the Portable Stimulus Standard (PSS), and for good reason because it could potentially save them time and effort in doing their jobs much better. In order to get the big picture on what PSS is all about I contacted Adnan Hamid, founder and CEO of Breker Verification Systems, because … Read More

The Practice of Low Power Design

For any given design objective, there is what we in the design automation biz preach that design teams should do, and then there’s what designs teams actually do. For some domains, the gap between these two may be larger than others, but we more or less assume that methodologies which have been around for years and are considered to… Read More

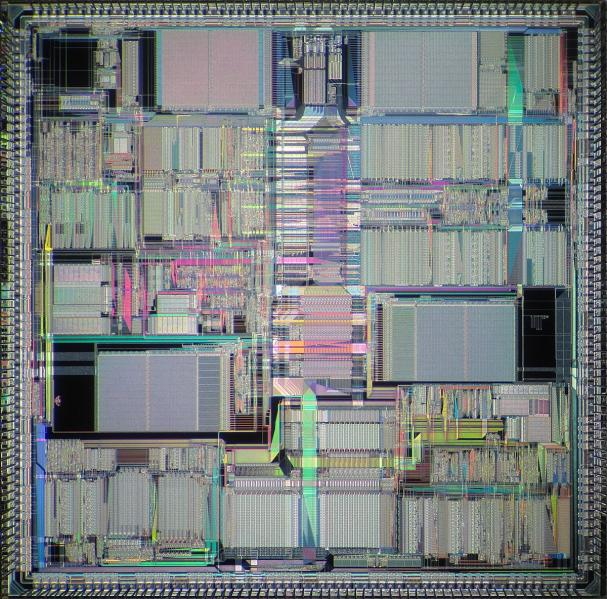

Is there anything in VLSI layout other than “pushing polygons”? (3)

In late 1986 the Layout Project Leader of DSP96000 got married and left for a 6 months’ vacation so I inherited the biggest chip MSIL had in stock. Floorplanning such size chip was a challenge from day one. Even the 68030 SUN workstation was too slow. I started to ask around and going to demos for any other possible tool that can help me… Read More

Finding the Right Needle in the IP Haystack

As the percentage of pre-configured IP increases in semiconductors, so design teams are able to reduce design cycle times. But one of the challenges for design teams is the inability to quickly and easily find IP because it’s incorrectly classified, sat in a designer’s home directory, or it’s been put into the ‘repository’ by an… Read More

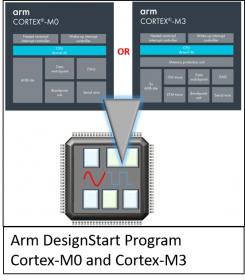

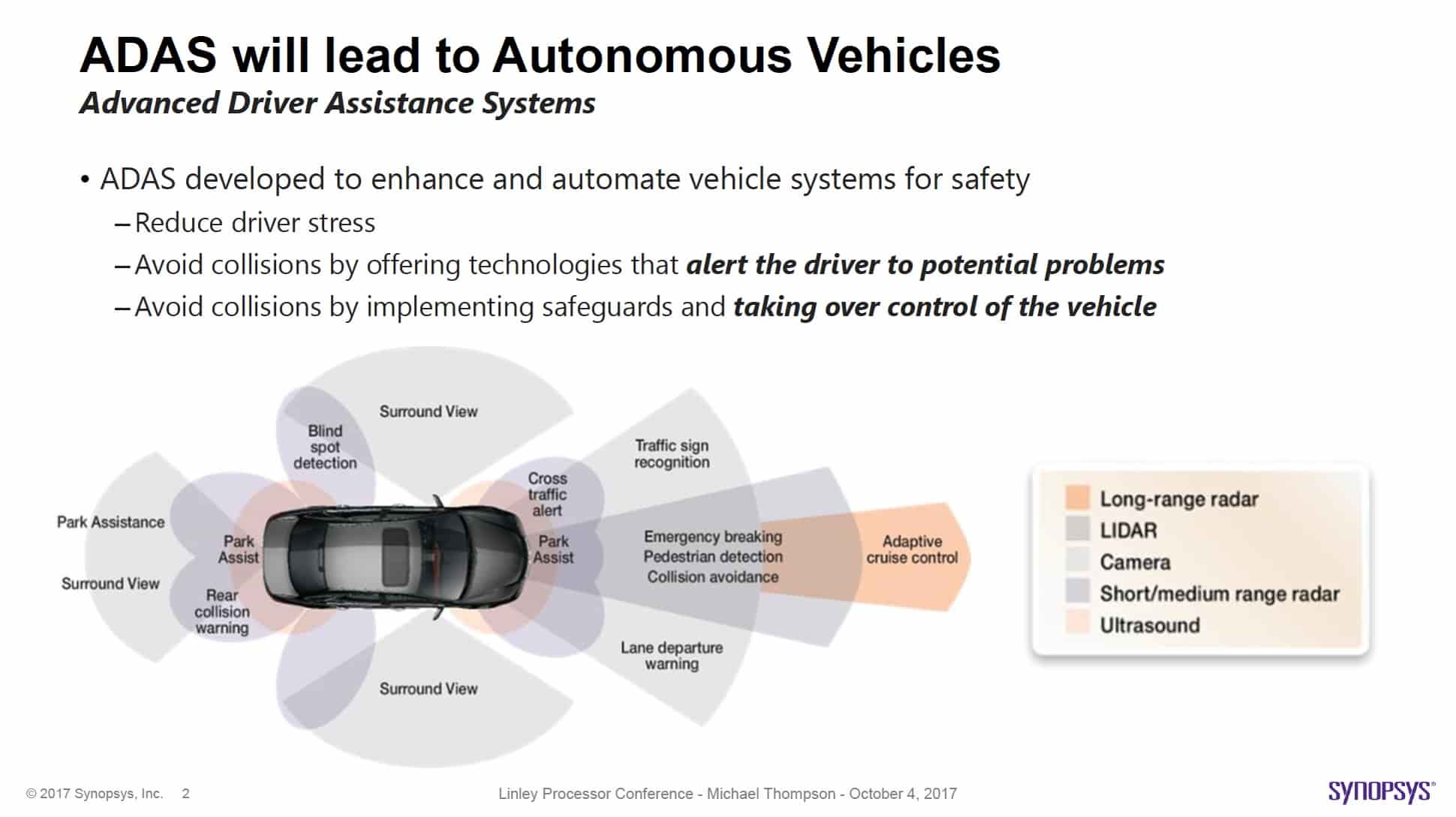

High performance processor IP targets automotive ISO 26262 applications

The reason you are seeing a lot more written about the ISO 26262 requirements for automotive electronics is, to put it bluntly, this stuff is getting real. Driver assist systems are no longer only found in the realm of Mercedes and Tesla, almost every car in every brand offers some driver assist features. However, the heavy lifting… Read More

The DIY Syndrome

When facing a new design objective, we check off all the established tools and flows we know we are going to need. For everything else, we default to an expectation that we will paper over the gaps with scripting, documentation and spreadsheets. And why not? When we don’t know what we will have to deal with, in documentation, scheduling,… Read More

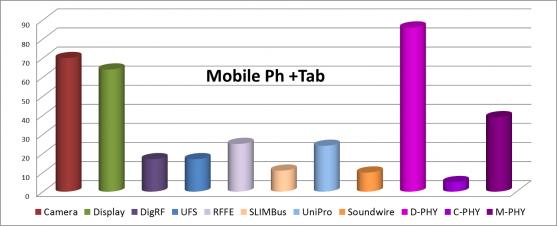

VESA DSC Encoder Enables MIPI DSI to Support 4K resolutions

Some of the MIPI specifications are now massively used in mobile (smartphone), like the Multimedia related specs, Camera Serial Interface (CSI-2) and Display Serial Interface (DSI). These specifications are now adopted inautomotive infotainment systems, and augmented reality (AR)/ virtual reality (VR) devices. If you … Read More

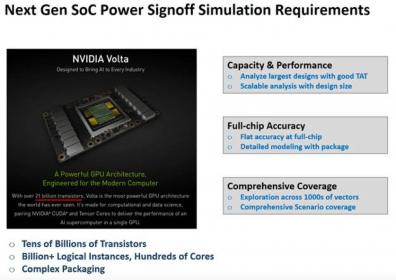

Webinar: High-Capacity Power Signoff Using Big Data

Want to know how NVIDIA signs off on power integrity and reliability on mega-chips? Read on.

PPA over-design has repercussions in increased product cost and potential missed schedules with no guarantee of product success. Advanced SoCs pack more functionality and performance resulting in higher power density, but traditional… Read More

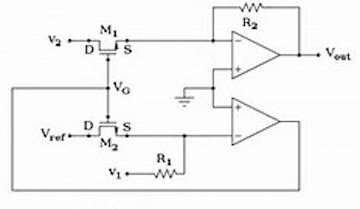

Webinars: Bumper Pack of AMS Webinars from ANSYS

Power integrity and reliability are just as important for AMS designs as they are for digital designs. Ansys is offering a series of five webinars on this topic, under a heading they call ANSYS in ACTION, a bi-weekly demo series from ANSYS in which an application engineer shows you how simulation can address common applications.… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center