When starting SemiWiki we focused on three market segments: EDA, IP, and the Foundries. Founding SemiWiki bloggers Daniel Payne and Paul McLellan were popular EDA bloggers with their own sites and I blogged about the foundries so we were able to combine our blogs and hit the ground running. For IP I recruited Dr. Eric Esteve who had… Read More

Electronic Design Automation

Converter Circuit Optimization Gets Powerful New Tool

DC converter circuit efficiency can have a big effect on the battery life of mobile devices. It also can affect power efficiency for wall-power operated circuits. Even before parasitics are factored in, converter circuit designers have a lot of issues to contend with. Optimizing circuit operation is essential for giving consumers… Read More

Semiconductor Specialization Drives New Industry Structure

When traveling the world there are the things that you see and the people that you meet. I have been very fortunate to meet some of the most amazing people and one of those people is Dr. Walden Rhines. Wally spent the first half of his career in semiconductors at TI and the second half in EDA with Mentor Graphics which gives him a cyborg … Read More

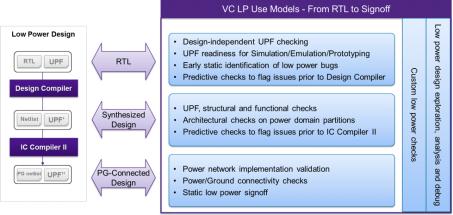

Low Power Verification Shifting Left

I normally think of shift left as a way to move functional verification earlier in design, to compress the overall design cycle. But it can also make sense in other contexts, one particularly important example being power intent verification.

If you know anything about power intent, you know that it affects pretty much all aspects… Read More

Cross View Static Validation

Improper handling of design validation could simply translate into a debugging exercise. In mainstream RTL2GDS flow, design implementation involves a top-level integration and lower-level block developments. These lower-level components, comprising of macros, IPs and standard cells are subjected to frequent abstraction… Read More

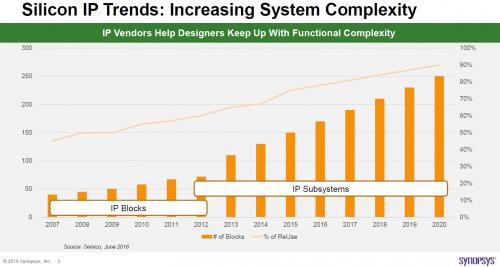

IP Vendor Tuning of Your SoC A Practice for Design Success

On April 17, Mick Posner, Director of Product Marketing, IP Subsystems, Hardening & IP Kit solutions held a Webinar entitled ‘Getting more from your IP Vendor, IP Tuned to Your SoC’. This brought back memories of the challenges in days past of making the right choices in IP selection, integration and validation when prudence… Read More

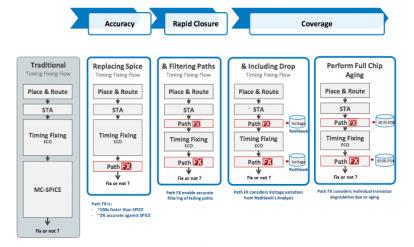

Peering Over the Timing Edge

I wrote recently about a yield problem which mobile vendors have been finding for devices built in advanced technologies. This was a performance issue (the devices worked fine at lower clock speeds), pointing to a discrepancy in some devices between predicted and observed timing. These were experienced design teams, using state… Read More

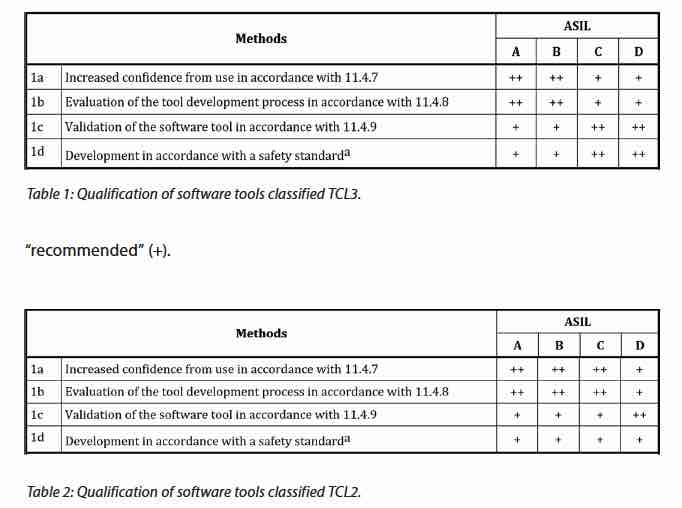

ISO 26262: Automotive electronics safety gets an update in 2018

In the field of automotive electronics, the year 2011 was a long time ago. So, it is about time that the initial ISO 26262 specification that was adopted back then gets an update. The latest version will be known as ISO26262:2018 and will expand the scope of the original to cover more types of vehicles. It will add an entire section on… Read More

2018 Women in Engineering Achievement Award

Having spent my entire thirty plus year career in semiconductors and design enablement I have seen quite a change in diversity. When I first started I remember thinking that height and weight was the only diversity here in Silicon Valley. My wife really noticed it when she attended her first Design Automation Conference in 1985 … Read More

Virtuoso at CDNLive – A Press Briefing With Yuval Shay

At CDNLive Silicon Valley 2018, I talked with Yuval Shay, Director of Product Management of Cadence Custom IC & PCB Group to scope out some more details on the recent Virtuoso product refresh announced earlier in the morning by Cadence Sr. VP & GM of the same group, Tom Beckley.

Tom shared his view on enabling the fourth industrial… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center