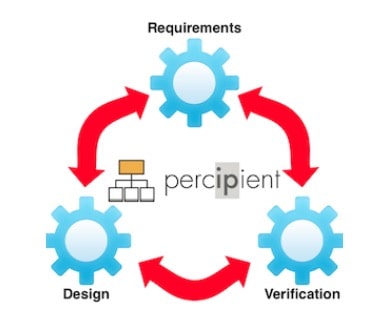

To me the major idea of ISO 26262 compliance is ensuring that requirements can be traced throughout the entire design and verification process, including the use of IP blocks. The first market application that comes to mind with ISO 26262 is automotive, with its emphasis on safety because human lives are at stake. Since necessity… Read More

Electronic Design Automation

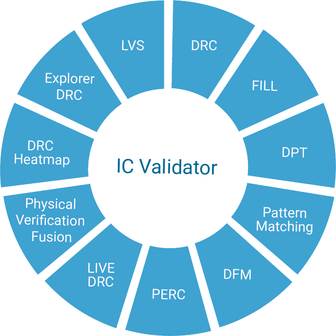

Complex Validation Requires Scalable Measures

The famous Olympic motto Citius, Altius, Fortius, which is the Latin words for “Faster, Higher, Stronger” to a considerable degree can be adapted to our electronics industry. Traditionally the fundamental metrics we used for measuring the quality of results (QoRs) are performance, power, and area (PPA). Amidst… Read More

Free Webinar: Analog Verification with Monte Carlo, PVT Corners and Worst-Case Analysis

The letters “PVT” roll of the tongue easily enough, belying the complexity that variations in process, temperature and voltage can cause for analog designs. For semiconductor processes, there are dozens of parameters that can affect the viability of a design. It would be easy enough to optimize a circuit with only one or two varying… Read More

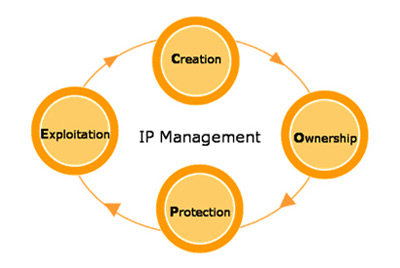

A Brief History of Methodics

Methodics has been a key player in IP management for over 10 years. In this section, Methodics shares their history, technology, and their role in developing IP Lifecycle Management (IPLM) solutions for the electronics industry.

Methodics is recognized as a premier provider of IP Lifecycle Management (IPLM) and traceability… Read More

EDA Update 2019

Over the last six years EDA has experienced yet another disruption not unlike the Synopsys acquisition of Avant! in 2001 which positioned Synopsys for the EDA lead they still enjoy today. Or the hiring of famed venture capitalist Lip-Bu Tan in 2009 to be the CEO of struggling EDA pioneer Cadence Design Systems. Under Lip-Bu’s… Read More

Deep Learning, Reshaping the Industry or Holding to the Status Quo

AI, Machine Learning, Deep Learning and neural networks are all hot industry topics in 2019, but you probably want to know if these concepts are changing how we actually design or verify an SoC. To answer that question what better place to get an answer than from a panel of industry experts who recently gathered at DVcon with moderator… Read More

A Brief History of IP Management

As RTL design started to increase in the late 1980’s and early 1990’s, it was becoming apparent that some amount of management was needed to keep track of all the design files and their associated versions. Because of the parallels to software development, design teams looked to the tools and methodologies that were in use by software… Read More

Foundational Excellence in a Laid-Back Style

I recently had a call with Rob Dekker, Founder and CTO of Verific. If you’re in EDA or semiconductor CAD, chances are high that you know who they are. They’re king of the hill in parser software for SystemVerilog and VHDL. When you hear a line like that, you assume a heavy dose of marketing spin, but here it really is fact. I don’t know of… Read More

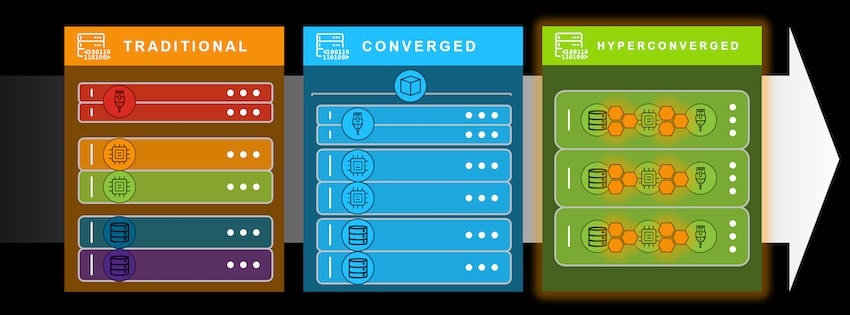

IC Implementation Improved by Hyperconvergence of Tools

Physical IC design is a time consuming and error prone process that begs for automation in the form of clever EDA tools that understand the inter-relationships between logic synthesis, IC layout, test and sign-off analysis. There’s even an annual conference called ISPD – International Symposium on Physical Design… Read More

Customizing and Standardizing IP with eSilicon at the Linley Conference

During the SoC Design Session at the just concluded Linley Spring Processor Conference in Santa Clara, Carlos Macian, Senior Director AI Strategy and Products at eSilicon, held a talk entitled ‘Opposites Attract: Customizing and Standardizing IP Platforms for ASIC Differentiation’.

Standardization is key to IP in modern … Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center