Whenever I am asked to explain how chip design works by someone who is unfamiliar with the process, I struggle to explain the different steps in the flow. It also makes me aware of the discrete separations between each phase of activities. Of course, when you speak to a novice it is not even possible to get more than one layer down in the… Read More

Electronic Design Automation

Best Practices for IP Reuse

As someone who was heavily involved with rules for IP reuse for many years, I have a major sense of déja vu in writing again on the topic. But we (in SpyGlass) were primarily invested in atomic-level checks in RTL and gate-level designs. There’s a higher level of best practices in process we didn’t attempt to cover. ClioSoft just released… Read More

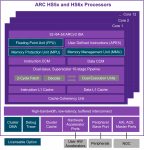

Synopsys is Changing the Game with Next Generation 64-Bit Embedded Processor IP

Synopsys issued a press release this morning that has some important news – Synopsys Introduces New 64-bit ARC Processor IP Delivering Up to 3x Performance Increase for High-End Embedded Applications. At first glance, one could assume this is just an announcement for some new additions to the popular ARC processor family. While… Read More

What’s New in CDC Analysis?

Synopsys just released a white paper, a backgrounder on CDC. You’ve read enough of what I’ve written on this topic that I don’t need to re-tread that path. However, this is tech so there’s always something new to talk about. This time I’ll cover a Synopsys survey update on numbers of clock domains in designs, also an update on ways to… Read More

UPDATE: Everybody Loves a Winner

Building a successful startup is hard, very hard. Creating a new category along the way is even more difficult. Those that succeed at both endeavors are quite rare. This is why an upcoming ESD Alliance event is a must-see in my view. The event is entitled “Jim Hogan and Methodics’ Simon Butler on Bootstrapping a Startup to Profitability… Read More

Private Datacenter Safer than the Cloud? Dangerously Wrong.

The irony around this topic in the middle of the coronavirus scare – when more of us are working remotely through the cloud – is not lost on me. Nevertheless, ingrained beliefs move slowly so it’s still worth shedding further light. There is a tribal wisdom among chip designers that what we do demands much higher security than any other… Read More

PSS, Test Realization and Reuse

Mentor just released a white paper on this topic which I confess has taxed my abilities to blog the topic. It’s not that the white paper is not worthy – I’m sure it is. I’m less sure that I’m worthy to blog on such a detailed technical paper. But I’m always up for a challenge, so let’s see what I can make of this, extracting a quick and not very… Read More

Mixed-Signal Debugging Gets a Boost

Having the right tool for the job at hand is always a joy, and when your IC project involves RTL code, gates, transistors and even parasitic interconnect, then you need some EDA tool help for debugging and finding out why your design behaves the way it is. An FAE named Sujit Roy did a conference call with me last week to show what StarVision… Read More

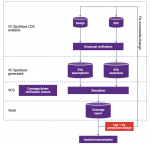

SpyGlass Gets its VC

It’s a matter of pride to me and many others from Atrenta days that the brand we built in SpyGlass has been so enduring. It seems that pretty much anyone who thinks of static RTL checking thinks SpyGlass. Even after Synopsys acquired Atrenta, they kept the name as-is, I’m sure because the brand recognition was so valuable.

Even good… Read More

Security in I/O Interconnects

I got a chance to chat with Richard Solomon at Synopsys recently about a very real threat for all of us and what Synopsys is doing about it. No, the topic isn’t the Coronavirus, it’s one that has been around a lot longer and will continue to be a very real threat – data and interconnect security.

First, a bit about Richard. He is the technical… Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era