You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

WP_Term Object

(

[term_id] => 157

[name] => EDA

[slug] => eda

[term_group] => 0

[term_taxonomy_id] => 157

[taxonomy] => category

[description] => Electronic Design Automation

[parent] => 0

[count] => 4439

[filter] => raw

[cat_ID] => 157

[category_count] => 4439

[category_description] => Electronic Design Automation

[cat_name] => EDA

[category_nicename] => eda

[category_parent] => 0

[is_post] =>

)

After an incredible year for SemiWiki I spent much of January breaking down 2020 with our sponsoring companies. Some had a down year, some had a flat year, but quite a few had remarkable years. One standout company is SmartDV which recorded a 51% revenue increase, so the important question is why?

Reasons:

SmartDV covers one of the… Read More

Let’s face it, AI is everywhere. From the cloud to the edge to your pocket, there is more and more embedded intelligence fueling efficiency and features. It’s sometimes hard to discern where human interaction ends, and machine interaction begins. The technology that underlies all this is quite complex and daunting to understand.… Read More

.The UVM standard was first released by Accellera 10 years ago this month and is now by far the leading methodology for functionally verifying logic designs, especially at the block level. As I write, DVCon fast approaches so I talked to Tom Fitzpatrick, Verification Technologist at Siemens EDA (Mentor Graphics) for a perspective.… Read More

Sathyam has over 35 years of experience in company management, R&D management and software development in Electronic Design Automation (EDA) (mostly) and PCB Manufacturing. He has headed companies, global engineering and marketing organizations in Forture-500 and in startups companies to introduce innovative and … Read More

Electromagnetic (EM) simulations have been performed on die metal structures since the 1990s. Originally, the analysis was restricted to a single device (e.g., a spiral inductor). The number of on-die devices simulated simultaneously grew with the increasing capabilities of the computers performing the computations. This… Read More

Mountains over 10,000 feet capped with snow in the winter. Some of the deepest, clearest blue sky you’ll find in the United States. Farmlands of green in the spring. That was the view looking out the second story window from the most awesome conference room I’ve ever taken a customer meeting. Even if I didn’t immediately understand… Read More

Machine learning (ML) is a once-in-a-generation innovation that seems like it should be applicable almost everywhere. It’s certainly revolutionized automotive safety, radiology and many other domains. In our neck of the woods, SoC implementation is advancing through learning to reduce total negative slacks and better optimize… Read More

As I’ve discussed before, HCL Compass is a very flexible tool to define and manage development and release processes at the enterprise level. In HCL’s own words: Low-code/no-code change management software for enterprise level scaling, process customization, and control to accelerate project delivery and increase developer… Read More

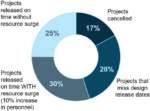

Although electronic systems design as a discipline has been around ever since electronics systems came into existence (and that was many decades ago), the design complexities involved and the demands and constraints placed on the systems have multiplied significantly since then. Recent research by LifeCycle Insights shows… Read More

The move from single-chip design to system-in-package design has created many challenges. The rise of 2.5D and 3D technology has set the stage for this. Beyond the modeling requirements and the need for ecosystem collaboration to get those models, there is a significant challenge in understanding the data. The only way to truly… Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era