The Electronic Design Automation (EDA) industry used to be a bustling bazaar of scrappy startups, along with medium sized companies that dominated a technology space, and big main-line vendors. The annual Design Automation Conference was noisy, hectic, and sprawled over multiple large convention halls. This diversity meant… Read More

Electronic Design Automation

Top 10 Takeaways from DAC 2021

The “in-person” portion of the Design Automation Conference (DAC) was recently held in San Francisco. (As several presenters were unable to attend, a “virtual” program is also available.) The presentations spanned a wide gamut – e.g., technical advanced in design automation algorithms; new features in commercial EDA tools; … Read More

DAC 2021 – Joe Sawicki explains Digitalization

Monday at DAC this year started off on a very optimistic note as Joe Sawicki from Siemens EDA presented in the Pavilion on the topic of Digitalization, a frequent theme in the popular press because of the whole Work From Home transition that we’ve gone through during the pandemic. Several industries are benefiting from the… Read More

A Practical Approach to Better Thermal Analysis for Chip and Package

Thermal modeling has become a hot topic for designers of today’s high-speed circuits and complex packages. This has led to the adoption of better and more sophisticated thermal modeling tools and flows as exemplified in this presentation by Micron at the IDEAS Digital Forum. The presentation is titled “Thermal Aware Memory Controller… Read More

Ansys CEO Ajei Gopal’s Keynote on 3D-IC at Samsung SAFE Forum

System on chip (SoC) based design has long been recognized as a powerful method to offer product differentiation through higher performance and expanded functionality. Yet, it comes with a number of limitations, such as high cost of development. Also, SoCs are monolithic, which can inhibit rapid adaptation in the face of changing… Read More

Effectively Managing Large IP Portfolios For Complex SoC Projects

In today’s world, no IC design is completed without instantiating a few or many pre-verified or already proven intellectual property (IP) blocks. With break-neck pace at which chip designs are advancing, many IP blocks may even be entire chip designs from earlier product releases. Third-party IP market has been growing at a healthy… Read More

Live 58th Design Automation Conference Coverage!

My beautiful first mate and I will be together at DAC this year. Her first DAC was 1985 in Las Vegas and we lived happily ever after. SemiWiki bloggers Tom Dillinger and Daniel Payne will also be at DAC attending sessions and meeting with exhibiting companies to learn and blog about the latest innovations inside the semiconductor … Read More

A Next-Generation Prototyping System for ASIC and Pre-Silicon Software Development

Every now and then, disruptive technology is brought to market, challenging the way things have been done to that point. We are all familiar with many such technologies. The rhetorical question is, how many of us were aware, recognized and acknowledged those technologies before they became well established? For example, a startup… Read More

Continuous Integration of RISC-V Testbenches

In my last blog post about AMIQ EDA, I talked with CEO and co-founder Cristian Amitroaie about their support for continuous integration (CI). We discussed in some detail how their Design and Verification Tools (DVT) Eclipse Integrated Development Environment (IDE) and Verissimo SystemVerilog Linter are used in CI flows. Cristian… Read More

Ansys to Present Multiphysics Cloud Enablement with Microsoft Azure at DAC

Ansys and Microsoft collaborated extensively over the past year to optimize and test Ansys’ signoff multiphysics simulation tools on the Azure cloud. Microsoft has invited Ansys to present the joint results in Azure’s DAC booth theater in San Francisco this year.

Two presentations are planned: covering the enablement of Ansys… Read More

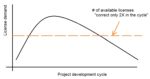

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era