According to the ESD Alliance, the single biggest revenue category in our industry is for semiconductor IP, so the concept of IP reuse is firmly established as a way to get complex products to market more quickly and reducing risk. On the flip side, with hundreds or even thousands of IP blocks in a complex SoC, how does a team, division… Read More

Electronic Design Automation

Prototype enables new synergy – how Artosyn helps their customers succeed

Artosyn Microelectronics, a leading provider of AI SoCs for drones and other sophisticated applications finds itself at the intersection of hardware architecture and software development. “Our customers are advancing the state of AI programming every day,” said Shen Sha, Senior R&D Manager of Artosyn’s AI Chip Department.… Read More

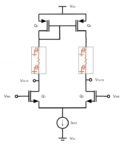

Analog IC Layout Automation Benefits

I viewed a recent webinar from Paul Clewes of Pulsic, and the topic was Balancing Analog Layout Parasitics in MOSFET Differential Pairs. This topic interests me, because back in 1982 I wrote my first IC layout automation tool at Intel that automatically created 15% of a GPU chip layout called the 82786, then joined Silicon Compilers… Read More

Non Volatile Memory IP is Invaluable for PMICs

Power Management ICs are a vitally important part of system design. Evidence of this is cited by a Synopsys white paper that mentions how Apple acquired a portion of PMIC developer Dialog Semiconductor that was previously their exclusive PMIC supplier. Clearly Apple had decided that PMIC design was a strategic differentiating… Read More

Using a GPU to Speed Up PCB Layout Editing

I can remember back in the 1980s how Apollo workstations were quite popular, because they accelerated the graphics display time for EDA tools much better than competitive hardware. Fast forward to 2022 and we have the same promise of speeding up EDA tools like PCB layout editing by using a GPU. At the 58th DAC there was a session called,… Read More

Breker Verification Systems Unleashes the SystemUVM Initiative to Empower UVM Engineering

The much anticipated (virtual) DVCON 2022 is happening this week and functional verification plus UVM is a very hot topic. Functional Verification Engineers using UVM can enjoy a large number of benefits by synthesizing test content for their testbenches. Abstract, easily composable models, coverage-driven content, deep… Read More

CEO Interview: Tamas Olaszi of Jade Design Automation

Why does the industry need another register management tool? This is a question that Tamas Olaszi, the founder of Jade Design Automation hears from time to time since Jade-DA brought Register Manager, their EDA tool, to market. So why?

There is a genuine answer to this question but first let me use this interview to give some helpful… Read More

Scalable Verification Solutions at Siemens EDA

Lauro Rizzatti recently interviewed Andy Meier, product manager in the Scalable Verification Solutions Division at Siemens EDA. Andy is a product manager in the Scalable Verification Solutions Division at Siemens EDA. Andy has held positions in the electronics and high-tech fields during his 20-year career including: Sr.… Read More

Working with the Unified Power Format

The Accellera organization created the concept of a Unified Power Format (UPF) back in 2006, and by 2007 they shared version 1.0 so that chip designers would have a standard way to communicate the power intentions of IP blocks and full chips. By 2009 the IEEE received the Accellera donation on UPF , reviewed multiple drafts and published… Read More

Power Analysis in Advanced SoCs. A Siemens EDA Perspective

The success of modern battery-powered products depends as much on useful operating time between charges as on functionality. FinFET process technologies overtook earlier planar CMOS in part because they significantly reduce leakage power. But they exacerbate dynamic power consumption thanks to increased pin capacitances.… Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era