Design re-use has enabled IC design teams to create billion-transistor designs where hundreds of IP blocks are pre-built from internal or external sources. Keeping track of where each of these IP blocks came from, what their version status is, managing IP, or even discerning their license status can be a full-time job if tracked… Read More

The Path to Chiplet Architecture

If you have anything to do with the semiconductor industry, you already know that one of the hottest areas for both manufacturing and EDA are systems designed with advanced packaging, basically putting more than one die (aka chiplets) in the same package.

When 3D packaging was first introduced, there were not really any effective… Read More

Synopsys Panel Updates on the State of Multi-Die Systems

Synopsys recently hosted a cross-industry panel on the state of multi-die systems which I found interesting not least for its relevance to the rapid acceleration in AI-centric hardware. More on that below. Panelists, all with significant roles in multi-die systems, were Shekhar Kapoor (Senior Director of Product Management,… Read More

Disaggregated Systems: Enabling Computing with UCIe Interconnect and Chiplets-Based Design

The world of computing is evolving rapidly, with a constant demand for more powerful and efficient systems. Generative AI has driven exponential growth in the amount of data that is generated and processed at very high data speeds and very low latencies. Traditionally, computing systems have been built using monolithic designs,… Read More

SPIE- EUV & Photomask conference- Anticipating High NA- Mask Size Matters- China

– SPIE EUV & Photomask conference well attended with great talks

– Chip industry focused on next gen High NA EUV & what it impacts

– Do big chips=big masks? Another Actinic tool?

– AI & chip tools, a game changer- China pre-empting more sanctions

The SPIE EUV & Photomask conference in Monterey

… Read MoreThe True Power of the TSMC Ecosystem!

The 15th TSMC Open Innovation Platform® (OIP) was held last week. In preparation we did a podcast with one of the original members of the TSMC OIP team Dan Kochpatcharin. Dan and I talked about the early days before OIP when we did reference flows together. Around 20 years ago I did a career pivot and focused on Strategic Foundry Relationships.… Read More

Keysight EDA 2024 Delivers Shift Left for Chiplet and PDK Workflows

Much of the recent Keysight EDA 2024 announcement focuses on high-speed digital (HSD) and RF EDA features for Advanced Design System (ADS) and SystemVue users, including RF System Explorer, DPD Explorer (for digital pre-distortion), and design elements for 5G NTN, DVB-S2X, and satcom phased array applications. Two important… Read More

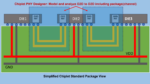

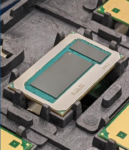

Intel Ushers a New Era of Advanced Packaging with Glass Substrates

Intel recently issued a press announcement that has significant implications for the future of semiconductors. The release announces Intel’s new glass substrate technology. The headline states: Glass substrates help overcome limitations of organic materials by enabling an order of magnitude improvement in design rules… Read More

Chiplets and IP and the Trust Problem

Perforce recently hosted a webinar on “IP Lifecycle Management for Chiplet-Based SoCs”, presented by Simon Butler, the GM for the Methodics IPLM BU. The central theme was trust, for IPs as much as chiplets. How can an IP/chiplet consumer trust that what they receive has not been compromised somewhere in the value chain from initial… Read More

Interface IP in 2022: 22% YoY growth still data-centric driven

We have shown in the “Design IP Report” 2022 that the market share of the wired Interface IP category is a growing part of the total IP, and that this trend is confirmed year after year. The interface IP category has moved from 18% share in 2017 to 25% in 2022.

During the 2010-decade, smartphone was the strong driver for the IP industry,… Read More

Siemens U2U 3D IC Design and Verification Panel