I wrote last year about the challenge Arm Client/Mobile faces in growing in a saturated phone market and how they put a big focus on mobile gaming to stimulate growth. The gaming direction continues but this year they have added (of course) an AI focus, not just to mobile but also to other clients, notably PCs. It would be easy to be cynical… Read More

Artificial Intelligence

Unlocking the Future: Join Us at RISC-V Con 2024 Panel Discussion!

Are you ready to dive into the heart of cutting-edge computing? RISC-V Con 2024 is just around the corner, and we’re thrilled to invite you to a riveting panel discussion that promises to reshape your understanding of advanced computing. On June 11th, from 4:00 to 5:00 PM, at the prestigious DoubleTree Hotel in San Jose, California,… Read More

The Fallacy of Operator Fallback and the Future of Machine Learning Accelerators

As artificial intelligence (AI) and machine learning (ML) models continue to evolve at a breathtaking pace, the demands on hardware for inference and real-time processing grow increasingly complex. Traditional hardware architectures for acceleration are proving inadequate to keep up with these rapid advancements in ML … Read More

Secure-IC Presents AI-Powered Cybersecurity

Design & Reuse held its IP-SoC Silicon Valley 24 event on April 25th, 2024, at the Hyatt Regency Santa Clara. The agenda was packed with many relevant and compelling presentations from companies large and small. I attended one presentation on security that stood out for me. Secure-IC presented “AI-powered cybersecurity:… Read More

Using LLMs for Fault Localization. Innovation in Verification

We have talked about fault localization (root cause analysis) in several reviews. This early-release paper looks at applying LLM technology to the task. Paul Cunningham (GM, Verification at Cadence), Raúl Camposano (Silicon Catalyst, entrepreneur, former Synopsys CTO and now Silvaco CTO) and I continue our series on research… Read More

Elevating Your SoC for Reconfigurable Computing – EFLX® eFPGA and InferX™ DSP and AI

Field-Programmable Gate Arrays (FPGAs) have long been celebrated for their unmatched flexibility and programmability compared to Application-Specific Integrated Circuits (ASICs). And the introduction of Embedded FPGAs (eFPGAs) took these advantages to new heights. eFPGAs offer on-the-fly reconfiguration capabilities,… Read More

AI System Connectivity for UCIe and Chiplet Interfaces Demand Escalating Bandwidth Needs

Artificial Intelligence (AI) continues to revolutionize industries, from healthcare and finance to automotive and manufacturing. AI applications, such as machine learning, deep learning, and neural networks, rely on vast amounts of data for training, inference, and decision-making processes. As AI algorithms become … Read More

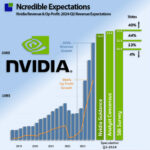

Ncredible Nvidia

This article previews Nvidia’s earnings release and will be updated during and after the earnings release. As usual, we will compare and contrast the Nvidia earnings with our supply chain glasses to identify changes and derive insights. Please return to this article, as it will be updated over the next week as we progress with our… Read More

Fully Automating Chip Design

Design Productivity Gap

Twenty-five years ago, SEMATECH first alerted the world to a concern known as the design productivity gap: the observation that the ability to manufacture complex chips had started outpacing the capability of designers to create them by more than a factor of two. This concern was subsequently reiterated… Read More

Anirudh Fireside Chats with Jensen and Cristiano

At CadenceLIVE 2024 Anirudh Devgan (President and CEO of Cadence) hosted two fireside chats, one with Jensen Huang (President and CEO of NVIDIA) and one with Cristiano Amon (President and CEO of Qualcomm). As you would expect both discussions were engaging and enlightening. What follows are my takeaways from those chats.

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era