For  decades, digital test has been fully automated including methodologies and automation for test pattern generation, grading and test time compression. Automation for analog and mixed-signal (AMS) IC test has not however kept pace. This is troubling as according to IBSapproximately 85% of SoC design starts are now AMS designs. Arguably nowhere are the issues of test and reliability being more keenly felt than in the automotive space with the advent of autonomous driving and advanced driver assistance systems (ADAS).

decades, digital test has been fully automated including methodologies and automation for test pattern generation, grading and test time compression. Automation for analog and mixed-signal (AMS) IC test has not however kept pace. This is troubling as according to IBSapproximately 85% of SoC design starts are now AMS designs. Arguably nowhere are the issues of test and reliability being more keenly felt than in the automotive space with the advent of autonomous driving and advanced driver assistance systems (ADAS).

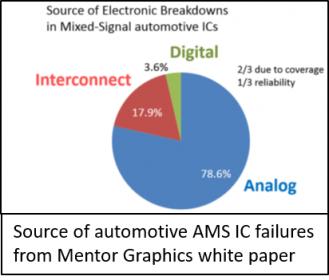

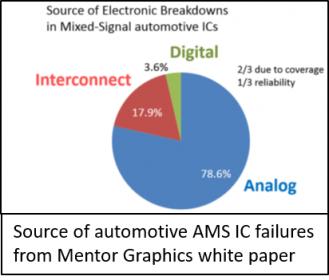

These systems all use analog sensors combined with AMS SoC processors to make complex real-time decisions. As reported by G. Gielen et.al. at the 2014 International Test Conference, more than 78% of electronic breakdowns in automotive AMS ICs were due to faults in the analog portions of these designs, two thirds of which were undetected at test due to the lack of adequate test coverage. Undetected faults in these types of circuits can make for someone having a very bad day when their car decides to turn left when it should have turned right. As if consequences of poor testing weren’t enough, AMS test is now dominating the total test time for these type ICs and that implies direct cost to IC suppliers, system designers and ultimately the consumer.

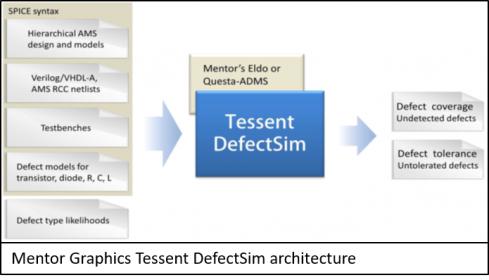

One of the reasons that AMS test hasn’t kept pace is the lack of an industry-accepted analog fault model. Additionally, excessive simulation times for even basic fault simulation on AMS circuits has kept the industry from progressing forward. This however may be changing with last weeks’ announcement by Mentor Graphics of their newTessent DefectSim product. Tessent DefectSim promises to dramatically improve productivity for both the grading of AMS test coverage and performing AMS fault simulation.

Fault Modeling

The first thing to realize is that the simple stuck-at fault models used for digital design are woefully inadequate for use in AMS designs. Mentor Graphics has an excellent white paper entitled ‘Analog Fault Simulation Challenges and Solutions’ describing this in detail but the quick version is that while shorts and opens certainly can and do affect AMS circuits, there are many more insidious parametric type faults that can affect an AMS circuit’s performance and functionality. Unfortunately, the number of the possible parametric faults is huge and the trick then becomes to select which faults to inject that will actually improve overall test coverage.

To make matters more complex, the likelihood of various types of faults happening is not equal. In digital design the difference in likelihood of a short and an open is not so large and thus ignored. This results in a weak but useable correlation between estimated fault coverage and actual reported defect rates. In AMS design this is not the case. The likelihood of different faults types varies widely and as a result, fault coverage tools must take this into account to get an accurate measure of test coverage.

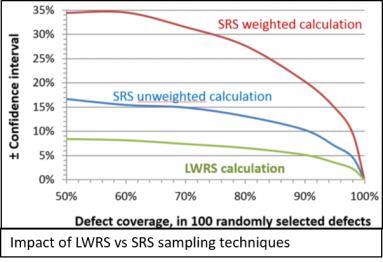

Tessent DefectSim uses a new method known as “likelihood-weighted random sampling” (LWRS). LWRS minimizes the number of defects to simulate by using something equivalent to a modified stratified-random sampling technique in which the likelihood of randomly selecting any given defect is proportional to the likelihood of the defect occurring. When the range of defect likelihoods is large, as it is for AMS circuits, LWRS requires up to 75% fewer samples than simple random sampling (SRS) for a given confidence interval, as the figure shows. In practice, when coverage is 90% or higher, this means that it is usually sufficient to simulate a maximum 250 defects, regardless of the circuit size or the number of potential defects, to estimate coverage within 2.5%, for a 99% confidence level. This ability to select effective faults goes a long way towards making for shorter more cost efficient test times.

Tessent DefectSim uses a new method known as “likelihood-weighted random sampling” (LWRS). LWRS minimizes the number of defects to simulate by using something equivalent to a modified stratified-random sampling technique in which the likelihood of randomly selecting any given defect is proportional to the likelihood of the defect occurring. When the range of defect likelihoods is large, as it is for AMS circuits, LWRS requires up to 75% fewer samples than simple random sampling (SRS) for a given confidence interval, as the figure shows. In practice, when coverage is 90% or higher, this means that it is usually sufficient to simulate a maximum 250 defects, regardless of the circuit size or the number of potential defects, to estimate coverage within 2.5%, for a 99% confidence level. This ability to select effective faults goes a long way towards making for shorter more cost efficient test times.

Additionally, DefectSim allows the designer to define custom defect models. For example, instead of injecting a simple stuck-on fault, a low threshold voltage and 50% wider gate could be injected. Or, instead of stuck-off, a high threshold voltage and 50% longer gate could be injected. Any test that identifies these two defect models will detect all six possible shorts and opens in a transistor. Thus, DefectSim allows the designer to use any of the classic defect models or create their own to specify shorts, opens, and variations of these models.

Fault Simulation Performance

Simulating every potential defect is however impractical unless simplifications are made. Simulators and designers already optimize simulation speed versus accuracy as much as possible for a given circuit. Therefore, any further speed up for fault simulation necessarily reduces accuracy and that can result in falsely-detected or falsely-undetected faults.

Tessent DefectSimworks with Mentor’s Eldoand Questa ADMS circuit simulators to measure the effects of opens, shorts, parametric variations, and user-defined defects modeled within a layout-extracted or schematic netlist. It employs a number of techniques to reduce total simulation time without reducing simulation accuracy or limiting the type of test. Examples of these techniques includes LWRS random sampling, high-level modeling, stop-on-detection, AC/DC mode, and parallel defect-based simulations. Mentor claims that all together, these techniques can reduce simulation time by up to six orders of magnitude compared to simulating the production test of all potential defects in flat, layout-extracted netlists while avoiding the pitfalls of previous approaches. Additionally, DefectSim aides in fault diagnosis by comparing voltage across injected faults to the voltage before the fault was injected to help designers diagnose whether a fault is undetected because the voltage across it has not been controlled by the test or because it has not been observed by the test.

Tessent DefectSimworks with Mentor’s Eldoand Questa ADMS circuit simulators to measure the effects of opens, shorts, parametric variations, and user-defined defects modeled within a layout-extracted or schematic netlist. It employs a number of techniques to reduce total simulation time without reducing simulation accuracy or limiting the type of test. Examples of these techniques includes LWRS random sampling, high-level modeling, stop-on-detection, AC/DC mode, and parallel defect-based simulations. Mentor claims that all together, these techniques can reduce simulation time by up to six orders of magnitude compared to simulating the production test of all potential defects in flat, layout-extracted netlists while avoiding the pitfalls of previous approaches. Additionally, DefectSim aides in fault diagnosis by comparing voltage across injected faults to the voltage before the fault was injected to help designers diagnose whether a fault is undetected because the voltage across it has not been controlled by the test or because it has not been observed by the test.

All in all, DefectSim appears to be a very impressive platform for defining and refining AMS test and should go a long way towards helping IC companies meet the demanding requirements of customers like automotive Tier 1 suppliers. For more information about Tessent DefectSim contact Steve Pateras, product marketing director at Mentor Graphics.

Share this post via:

Comments

0 Replies to “Mentor DefectSim Seen as Breakthrough for AMS Test”

You must register or log in to view/post comments.