The growth of complexity for silicon test as it relates to test data volume and test times is driven by multiple concurrent factors. One dimension is simply the increase in silicon complexity. However, other factors are playing a role as well. These include higher reliability requirements for new applications such as automotive, aerospace and defense. These requirements have not only increased test challenges at the point of manufacture, but also are moving incipient test challenges to system assembly and assembled products in the field. Approaches that worked before are reaching their practical limits and new silicon lifecycle management test requirements are being tackled for the first time.

To address these multiple issues Synopsys has developed an IP that allows the use of high-speed functional interfaces that already exist on chips for accessing the test network. This eliminates the need to set aside dedicated pins. This is especially true with high speed functional interfaces operating at speeds higher than test pins. Benefits of this approach are reduced pin count, less need for specialized test equipment, higher data rates and the ability to access test functionality at all phases of an SOC’s lifecycle.

Let’s dig into the details of this interesting shift in thinking. Many of us painfully remember when there were unique and specific interfaces for keyboards, hard drives, displays, pointers, printers, interface cards and the like. Once interfaces like USB and PCIe came along, it became obvious that consolidation made sense. Today’s SOCs all utilize interfaces such as USB and PCIe which can run at high speeds, so why not leverage as test access ports too? Furthermore, the IEEE 1149.10 specification approved in 2017 creates a standard for packetizing test data which can be moved through existing high-speed interfaces.

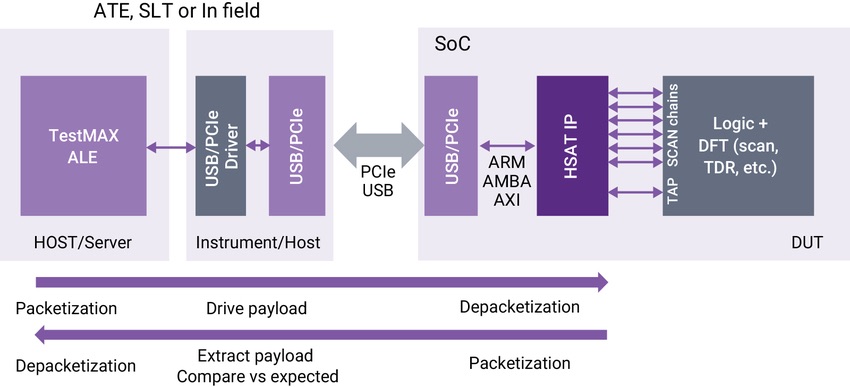

Synopsys is working on supporting 1149.10 protocol. TestMAX ALE test software from Synopsys pairs with SiliconMAX HSAT IP to provide a complete solution. Synopsys TestMAX ALE can run on testers, PCs or SLT platforms, doing ATPG pattern translation for data feeding into the SoC and reverse mapping for the data being collected from the SOC. SiliconMAX HSAT IP has the capability to support variety of interfaces like PCIe, USB, SPI, MIPI, 1149.10, etc.

SiliconMAX HSAT IP supports full test functionality. It handles data format translation, packetizing and depacketizing. It also conveys the test data and commands to the SOC’s DFT logic. Chips that use the SiliconMAX HSAT IP for test no longer need dedicated test pins. Time required to move data is reduced due to higher data rates of the functional interface. Plus, increased flexibility allows for improved reliability by supporting test throughout the entire lifecycle of the chip.

The SiliconMAX HSAT IP comes with the full set of collaterals needed to integrate it into a design. It uses a configurable ARM AMBA AXI slave interface to connect to the functional interface. Also included is ARM AMBA AXI loopback testbench generation. It also comes with configurable scan chains (512 max) and a TAP. There is an optional EBC interface for USB to enable DMA function. An added benefit is that SiliconMAX HSAT IP can also provide access to silicon monitoring network on SOCs.

Using existing high-speed interfaces for solves several important issues for SOC designers. It reduces or eliminates the need for dedicated pins and offers higher speed access to on chip scan and test resources. But perhaps most importantly it opens the door to improved silicon lifecycle management which is essential for many rapidly growing application areas, such as automotive. More information on SiliconMAX HSAT IP can be found here on the Synopsys website.

Also read:

Non Volatile Memory IP is Invaluable for PMICs

Why It’s Critical to Design in Security Early to Protect Automotive Systems from Hackers

Identity and Data Encryption for PCIe and CXL Security

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.