MIPI may have started out as a standard for mobile phones, but it has become very important for connecting cameras and displays in a wide range of other things such as cameras, computers, drones, VR glasses, IoT devices and cars. Along the way it has matured by adding important features to support new applications. Now when we talk about vision processing systems, we need to include AI and a much wider set of devices for capture and display. Phones often have multiple cameras with very high resolution. Displays can include rear view mirrors, goggles, or ADAS displays. Integration of MIPI into SoCs has been made much easier with the availability of IP such as Synopsys MIPI IP.

To help make sense of all the advances and applications of MIPI to these systems, Synopsys has produced a webinar on the topic of “How to Use MIPI Interfaces to Accelerate Camera and Display SoC Designs” hosted by Licinio Sousa, Product Marketing Manager at Synopsys. I’ll say that in all the time I have been covering MIPI, his presentation of the technology is one of the clearest and most comprehensive that I have seen. It covers camera and display market trends, what’s new in MIPI CSI-2 and DSI/DSI-2 and closes with a discussion of Synopsys MIPI IP for automotive applications.

Camera sensors are being built with increasing resolutions, sometimes upwards of 100 mega-pixels. They are also becoming AI enabled for specific tasks such as facial or object recognition. The number of vision sensors in systems is also increasing dramatically. Cars may have 10 to 30 cameras. At the same time displays have diversified. Systems may have multiple displays, foldable displays, and very high resolutions. We see displays on appliances, and they are going to be used for rear and side view mirrors etc.

Licinio explains in the webinar that for cameras we have CSI-2 and either D-PHY or C-PHY. On the display side we have DSI/DSI-2 with D-PHY or C-PHY. Licinio starts with the PHYs. D-PHY is the older PHY with up to 4.5 Gbps as of the October 2019 version 2.5. It uses source synchronous differential pairs for each lane. The number of lanes can be increased to improve throughput. D-PHY also offers a low power single ended connection for control and status.

C-PHY uses a completely different approach to handle higher bandwidth. C-PHY uses trios with three phase encoding and embedded clock. The Tx is single ended, but the Rx is differential, using combinations of the lines. Further decoding is necessary, but overall the result is higher throughput and better power efficiency. The bitrate is ~2.28X the signaling rate. The current spec for C-PHY from September 2019 is version 2.0 which supports 6 Gsps per trio. Licinio does an excellent job of discussing how the PHY layer works.

With similar electrical specs between the D-PHY and C-PHY it is possible to offer backwards compatibility over connections. Most of the PHY layer circuits can be reused. With 10 pins it is possible to switch between 4 lanes of D-PHY or 3 trios of C-PHY.

Licinio also discusses the important features that have been added in each newer version of the camera and display interface. On the camera side many new features have been added beyond those found in the original CSI-2 V1.x which supported mobile phones with lower resolutions and frames per second. Later additions to the spec have included virtual channels, interference reduction, latency reduction, compression and raw modes. The latest version boasts always-on monitoring, functional safety, longer channels and security. For the display side in going from DSI-V1.x to DSI-2 V1.1 and V1.2 there have been additions for functional safety, compression, content protection, functional safety and more.

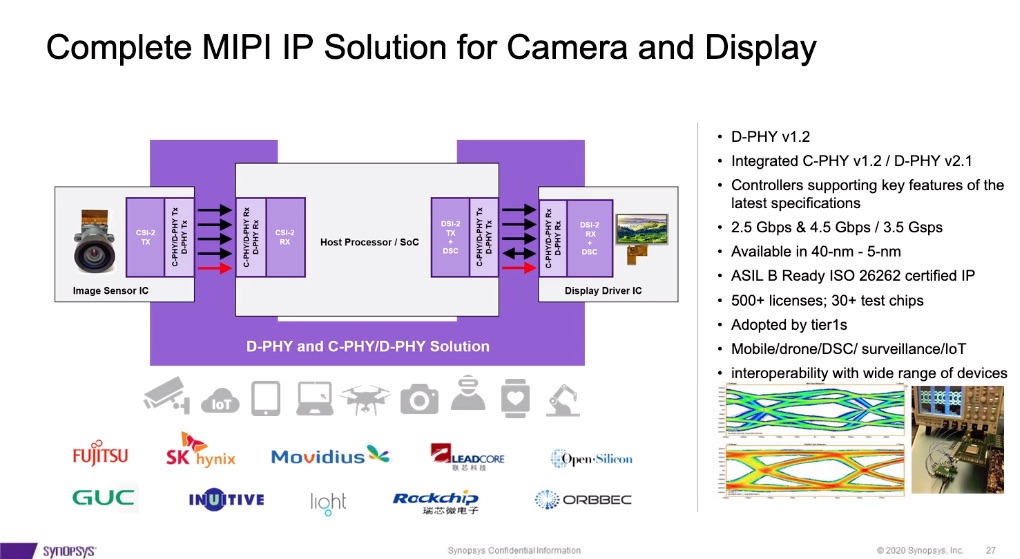

Licinio wrapped up with a summary of the Synopsys MIPI IP , including C-PHY, D-PHY, CSI-2, and DSI & DSI-2. With these they can support a wide range of use cases, including consumer, industrial vision, edge/AI, automotive, and more. In particular they their offering is ASIL-B ready and the PHYs are AEC-Q100 compliant. Their automotive MIPI IP is available in 22nm, 16nm, and 7nm. As I mentioned above this webinar offers a thorough look at MIPI and the solutions available from Synopsys for SoC integration. The complete webinar is available for viewing on the Synopsys website.

Also Read:

Synopsys talks about their DesignWare USB4 PHY at TSMC’s OIP

AI/ML SoCs Get a Boost from Synopsys IP on TSMC’s 7nm and 5nm

Parallel-Based PHY IP for Die-to-Die Connectivity

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.