I love reading about the amazing progress of autonomous vehicles, like when Audi and their A8 model sedan was the first to reach Level 3 autonomy, closely followed by Tesla at Level 2, although Tesla gets way more media attention here in the US. A friend of mine bought his wife a car that offers adaptive cruise control with auto-braking, as needed. All of these cool and life-saving features from the ever-increasing levels of automotive automation are made possible only through advanced silicon, sensors, radar, lidar, firmware and software.

For SoC chip design teams the risks and rewards are huge, but the biggest rewards likely will go to the companies that get their new IC designs into silicon first, so the race is on, and one big part of the engineering schedule continues to be pre-silicon verification. The only way to verify is to model and then extensively run simulations for all features and scenarios.

Software-based simulation is always a good starting point for verification, because it’s a mature technology and familiar to the majority of engineers, but the downside is that the larger the SoC and the more scenarios required the longer the runtimes, until the approach becomes infeasible because of time constraints. Our industry has an answer for meeting those verification time constraints, and that is from using a hardware-based approach with emulation.

Attending DAC in 2019, plus daily reading of news headlines and my LinkedIn feed, I have learned three mega-trends in the automotive market segment:

- Forecasted increase of $7 trillion by 2050, fortune.com

- Domain controllers are replacing ECUs and micro-controllers

- Safety is paramount, so standards like NCAP safety ratings are important

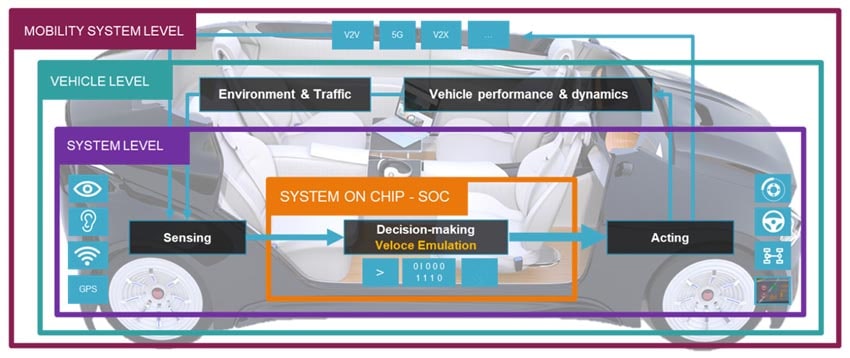

Increased complexity in automotive systems is creating bigger verification demands for SoC verification. To reach Level 5 autonomy requires car makers to have systems using multiple CPUs, AI engines and image processors. These systems are controlled by sophisticated software, requiring verification for functional correctness plus meet safety standards described by ISO 26262.

Car companies will need to debug the source of hardware and software bugs during testing and verification, so the quicker the better.

There are three verification phases to consider in designing SoCs for automotive use:

- Model-in-the-loop (MiL), using high-level models

- Plus: speed, capacity

- Minus: accuracy

- Software-in-the-loop (SiL), using logic simulation

- Plus: accurate, debugging

- Minus: speed, capacity

- Hardware-in-the-loop (HiL), using emulation

- Plus: speed, capacity

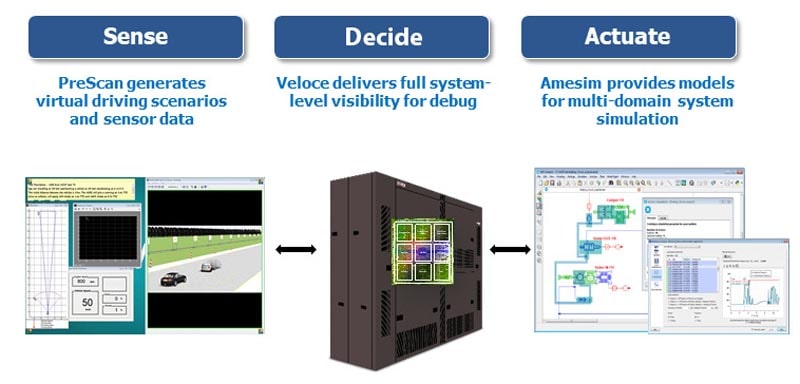

Siemens PLM Software already has a vehicle design and verification program called PAVE360, and within that the IC design part uses the Veloce emulator. Attending DAC this summer I noticed that Mentor and other vendors all prominently displayed their emulators, because of how important they are to verification of the most complex systems. The more that a system relies on software, the more likely it is that you will adopt emulation for verification.

Why emulation? Well, mostly speed and capacity, so running 1,000X to 10,000X faster on a specialized emulator compared to a logic simulator is a compelling methodology. The emulator gets this speed advantage by using a hardware fabric that can be reconfigured for each new SoC design to be verified, enabling engineers to actually run software and an operating in a reasonable amount of time.

So what’s attractive about the emulation from Veloce?

- Maturity, many years of improving results

- Integration

- Vista/SystemC (multi-physics, high-level modeling)

- Amesim (electro-mechanical)

- PAVE360 (scenarios)

- Verification IP (VIP) library

- Capacity of 15 billion logic gates

- Debug visibility

- Automotive specific applications

- Power verification

- Meeting functional safety requirements

Summary

I eagerly await Level 5 autonomous driving, and between now and then will closely watch the growth in this exciting industry because of the safety and wow factors. Behind the scenes I expect more design companies in this segment to adopt hardware emulation like Veloce in order to meet their time window, produce the most safe vehicle controls and enable both hardware and software debug. Mentor has assembled a compelling collection to serve the automotive design market.

Read the full size page White Paper here.

Related Blogs

- A Update from Joe Sawicki @ Mentor, a Siemens Business 56th DAC

- User2User Silicon Valley 2019

- Mentor Showcases Digital Twin Demo

- Verifying Software Defined Networking

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center